Arm<sup>®</sup> Platform Security Architecture Trusted Base System Architecture for Arm<sup>®</sup>v6-M, Arm<sup>®</sup>v7-M and Arm<sup>®</sup>v8-M 2.0

| Document number: | DEN 0083         |

|------------------|------------------|

| Release Quality: | Beta             |

| Release Number:  | 2                |

| Confidentiality  | Non-Confidential |

| Date of Issue:   | 13/12/2019       |

© Copyright Arm Limited 2017-2019. All rights reserved.

# Contents

| Abou | it this do | ocument                                                                                    | v                     |

|------|------------|--------------------------------------------------------------------------------------------|-----------------------|

|      | Release    | e Information                                                                              | v                     |

|      | Arm No     | on-Confidential Document Licence ("Licence")                                               | vii                   |

|      | Refere     | nces                                                                                       | ix                    |

|      | Terms      | and abbreviations                                                                          | х                     |

|      | Feedba     | ack<br>Feedback on this book                                                               | <b>xii</b><br>xii     |

| 1    |            | Introduction [Informative]                                                                 | 13                    |

|      | 1.1        | Scope                                                                                      | 14                    |

|      | 1.2        | Organization of the document                                                               | 14                    |

|      | 1.3        | Target Platforms1.3.1Level of protection                                                   | <b>14</b><br>15       |

|      | 1.4        | Security Development Lifecycle                                                             | 15                    |

|      | 1.5        | Compliance                                                                                 | 16                    |

|      | 1.6        | Scope and intended Audience                                                                | 17                    |

| 2    |            | Trustworthy networked devices [Informative]                                                | 17                    |

|      | 2.1        | Use Cases<br>2.1.1 Secure machine to machine communication<br>2.1.2 Secure firmware update | <b>17</b><br>17<br>18 |

|      | 2.2        | Security goal                                                                              | 18                    |

|      | 2.3        | Security analysis                                                                          | 19                    |

| 3    |            | Platform Security Architecture concepts [Informative]                                      | 19                    |

|      | 3.1        | Security by separation                                                                     | 19                    |

|      | 3.2        | Trusted and Non-Trusted worlds                                                             | 20                    |

|      | 3.3        | PSA software architecture                                                                  | 20                    |

| 4    |            | Hardware supported isolation [Informative]                                                 | 22                    |

| 4.1 | TrustZone-based isolation                                                    | 22       |

|-----|------------------------------------------------------------------------------|----------|

| 4.2 | MPU-based isolation                                                          | 25       |

| 4.3 | Dual PE-based isolation                                                      | 26       |

| 4.4 | Custom-logic based isolation                                                 | 28       |

| 4.5 | Trusted subsystems                                                           | 29       |

| 4.6 | PSA isolation levels                                                         | 33       |

| 4.7 | Basic architecture                                                           | 34       |

| 4.8 | Assisted architecture                                                        | 35       |

|     | TBSA-M security requirements [Normative]                                     | 35       |

| 5.1 | System view                                                                  | 36       |

| 5.2 | Infrastructure                                                               | 37       |

|     | 5.2.1 Memory system                                                          | 37       |

|     | 5.2.2 Shared volatile storage                                                | 40       |

|     | 5.2.3 Interrupts                                                             | 40       |

|     | 5.2.4 Secure RAM<br>5.2.5 Power and clock management                         | 41       |

|     | <ul><li>5.2.5 Power and clock management</li><li>5.2.6 Peripherals</li></ul> | 42<br>42 |

| 5.3 | Fuses                                                                        | 44       |

| 5.4 | Cryptographic keys                                                           | 46       |

|     | 5.4.1 Cryptographic schemes                                                  | 47       |

|     | 5.4.2 Static and ephemeral keys                                              | 47       |

|     | 5.4.3 Device unique and common keys                                          | 48       |

|     | 5.4.4 Source                                                                 | 48       |

|     | 5.4.5 Root keys                                                              | 49       |

| 5.5 | Trusted boot                                                                 | 50       |

|     | 5.5.1 Overview                                                               | 50       |

|     | 5.5.2 Boot types                                                             | 51       |

|     | 5.5.3 Boot configuration                                                     | 51       |

|     | 5.5.4 Stored configuration                                                   | 52       |

|     | 5.5.5 Secure lockdown                                                        | 52       |

|     | 5.5.6 Assisted architecture                                                  | 53       |

| 5.6 | Trusted timers                                                               | 53       |

|     | 5.6.1 Trusted clock source                                                   | 53       |

|     | 5.6.2 General Trusted timer                                                  | 53       |

|     | 5.6.3 Watchdog                                                               | 53       |

|     | 5.6.4 Trusted time                                                           | 54       |

5

|     | 5.7      | Version counters                          | 55 |

|-----|----------|-------------------------------------------|----|

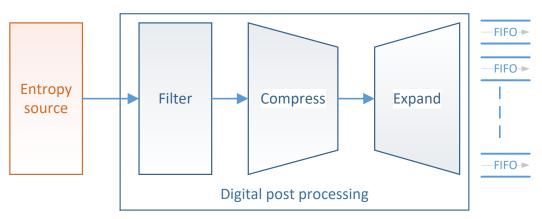

|     | 5.8      | Entropy source                            | 56 |

|     | 5.9      | Cryptographic acceleration                | 58 |

|     | 5.10     | Debug                                     | 59 |

|     |          | 5.10.1 Protection mechanisms              | 59 |

|     |          | 5.10.2 Debug Protection Mechanism overlap | 60 |

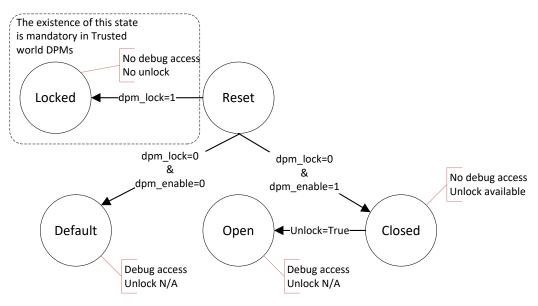

|     |          | 5.10.3 Debug Protection Mechanism states  | 60 |

|     |          | 5.10.4 Unlock operations                  | 62 |

|     |          | 5.10.5 Other debug functionality          | 64 |

|     |          | 5.10.6 Arm debug implementation           | 64 |

|     |          | 5.10.7 Basic architecture                 | 64 |

|     |          | 5.10.8 Assisted architecture              | 65 |

|     |          | 5.10.9 Unprivileged Debug Extension       | 65 |

|     | 5.11     | External interface peripherals            | 65 |

|     | 5.12     | DRAM protection                           | 66 |

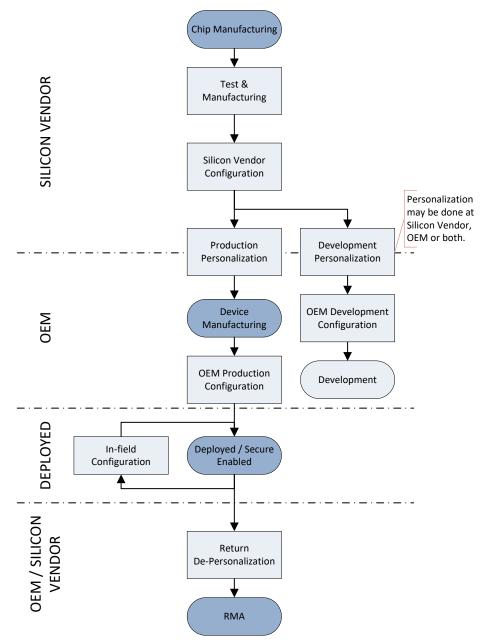

| 6   |          | Device lifecycle management [Normative]   | 66 |

| 7   |          | Cryptography requirements [Normative]     | 69 |

| 8   |          | Related documents                         | 70 |

| Арр | endix: T | BSA-M checklist [Normative]               | 70 |

# About this document

### **Release Information**

The change history table lists the changes that have been made to this document.

| Date           | Version     | Confidentiality  | Change                                                                                                                            |

|----------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| December 2019  | 2.0 Beta 0  | Non-Confidential | Updated what TBSA-M compliance means with respect to the requirements and the SDL. This is done in the Introduction (section 1.5) |

|                |             |                  | Updated Cryptography requirements (Chapter 7) from NIST Suite B to CNSA and referred to other national standards.                 |

|                |             |                  | Replaced R220_TBSA_DEBUG with a recommendation.                                                                                   |

|                |             |                  | Many editorial changes to the text: clarifications, typographical and stylistic.                                                  |

|                |             |                  | Several clarifications to the wording of requirements.                                                                            |

|                |             |                  | Added recommendations for dealing with Armv8-M UDE support (section 5.10.9).                                                      |

|                |             |                  | Updated references to NIST (page ix).                                                                                             |

| February 2019  | 1.1 Beta    | Non-Confidential | Several re-wordings and fixing of typographical errors.                                                                           |

| October 2018   | 1.0 Beta 0  | Non-Confidential | Updated cryptographic References                                                                                                  |

|                |             |                  | Added support for Ed25519                                                                                                         |

| September 2018 | 1.0 Alpha 0 | Confidential     | Aligned document context with other PSA documents                                                                                 |

|                |             |                  | Removed most threat modelling description (PSA-SM to cover this)                                                                  |

|                |             |                  | Modified many sentences to clarify based on internal feedback                                                                     |

|                |             |                  | Added Labelling of each chapter as either<br>[Informative] or [normative]                                                         |

|                |             |                  | Added section 1.2 which describes the document organization                                                                       |

|                |             |                  | Removed PSA readiness chapter (out of line with current PSA intentions)                                                           |

| June 2018      | 1.0 Dev 0   | Confidential     | Fork from TBSA Armv8-M (DEN 0062A)                                                                                                |

|                |             |                  | Adding:                                                                                                                           |

|                |             |                  | non-TrustZone isolation mechanisms (Chapter 4)                                                                                    |

Use of Hardware Anchors, for example secure elements and secure enclaves (Section 4.5)

2 new requirements (R001\_TBSA\_BASE and R002\_TBSA\_BASE)

Modifying:

Context referring to PSA firmware framework and security model

Existing text (in requirements) so that it does not rely solely on TrustZone for Armv8-M

Removed PSA Readiness chapter

# Arm<sup>®</sup> Platform Security Architecture Trusted Base System Architecture for Arm<sup>®</sup>v6-M, Arm<sup>®</sup>v7-M and Arm<sup>®</sup>v8-M

Copyright ©2017-2019 Arm Limited or its affiliates. All rights reserved. The copyright statement reflects the fact that some draft issues of this document have been released, to a limited circulation.

### Arm Non-Confidential Document Licence ("Licence")

This Licence is a legal agreement between you and Arm Limited ("**Arm**") for the use of the document accompanying this Licence ("**Document**"). Arm is only willing to license the Document to you on condition that you agree to the terms of this Licence. By using or copying the Document you indicate that you agree to be bound by the terms of this Licence. If you do not agree to the terms of this Licence, Arm is unwilling to license this Document to you and you may not use or copy the Document.

This Document is **NON-CONFIDENTIAL** and any use by you is subject to the terms of this Licence between you and Arm.

Subject to the terms and conditions of this Licence, Arm hereby grants to you under the intellectual property in the Document owned or controlled by Arm, a non-exclusive, non-transferable, non-sub-licensable, royalty-free, worldwide licence to:

- (i) use and copy the Document for the purpose of designing and having designed products that comply with the Document;

- (ii) manufacture and have manufactured products which have been created under the licence granted in (i) above; and

- (iii) sell, supply and distribute products which have been created under the licence granted in (i) above.

# You hereby agree that the licences granted above shall not extend to any portion or function of a product that is not itself compliant with part of the Document.

Except as expressly licensed above, you acquire no right, title or interest in any Arm technology or any intellectual property embodied therein.

THE DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. Arm may make changes to the Document at any time and without notice. For the avoidance of doubt, Arm makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

NOTWITHSTANING ANYTHING TO THE CONTRARY CONTAINED IN THIS LICENCE, TO THE FULLEST EXTENT PETMITTED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, IN CONTRACT, TORT OR OTHERWISE, IN CONNECTION WITH THE SUBJECT MATTER OF THIS LICENCE (INCLUDING WITHOUT LIMITATION) (I) LICENSEE'S USE OF THE DOCUMENT; AND (II) THE IMPLEMENTATION OF THE DOCUMENT IN ANY PRODUCT CREATED BY LICENSEE UNDER THIS LICENCE). THE EXISTENCE OF MORE THAN ONE CLAIM OR SUIT WILL NOT ENLARGE OR EXTEND THE LIMIT. LICENSEE RELEASES ARM FROM ALL OBLIGATIONS, LIABILITY, CLAIMS OR DEMANDS IN EXCESS OF THIS LIMITATION.

This Licence shall remain in force until terminated by you or by Arm. Without prejudice to any of its other rights, if you are in breach of any of the terms and conditions of this Licence then Arm may terminate this Licence immediately upon giving written notice to you. You may terminate this Licence at any time. Upon termination of this Licence by you or by Arm, you shall stop using the Document and destroy all copies of the Document in your possession. Upon termination of this Licence, all terms shall survive except for the licence grants.

The Document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of the Document complies fully with any relevant export laws and regulations to assure that the Document or any portion thereof is not exported, directly or indirectly, in violation of such export laws.

If any of the provisions contained in this Licence conflict with any of the provisions of any click-through or signed written agreement with Arm relating to the Document, then the click-through or signed written agreement prevails over and supersedes the conflicting provisions of this Licence. This Licence may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this Licence and any translation, the terms of the English version of this Licence shall prevail.

The Arm corporate logo and words marked with  $^{\circ}$  or  $^{m}$  are registered trademarks or trademarks of Arm (or its subsidiaries) in the EU, US and/or elsewhere. All rights reserved. No licence, express, implied or otherwise, is granted to you under this Licence, to use the ARM trade marks in connection with the Document or any products based thereon.

The validity, construction and performance of this Licence shall be governed by English Law.

Copyright © 2018 Arm Limited (or its affiliates). All rights reserved.

Arm Limited. Company 02557590 registered in England. 110 Fulbourn Road, Cambridge, England CB1 9NJ.

Arm document reference: LES-PRE-21585

# References

This document refers to the following documents.

| Ref  | Document<br>Number       | Title                                                                                                                                                                                  |

|------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]  | PRD29<br>GENC<br>009492C | Arm Security Technology - Building a Secure System using TrustZone<br>Technology                                                                                                       |

| [2]  | ARM DDI<br>00553A.b      | Armv8-M Architecture Reference Manual                                                                                                                                                  |

| [3]  | ARM DEN<br>0006B         | Arm Trusted Board Boot Requirements                                                                                                                                                    |

| [4]  |                          | Trusted Firmware-A                                                                                                                                                                     |

| [5]  | ARM ECM<br>0437502       | TrustZone Technology Microcontroller System Hardware Design<br>Concepts.                                                                                                               |

| [6]  | ARM DEN<br>0021C         | Arm Trusted Base System Architecture, CLIENT                                                                                                                                           |

| [7]  | ARM DEN<br>0063          | PSA Firmware Framework – M-profile                                                                                                                                                     |

| [8]  | ARM DEN<br>0072          | PSA Trusted Boot and Firmware Update                                                                                                                                                   |

| [9]  | ARM ECM<br>0390891       | PSA: Device Security Model                                                                                                                                                             |

| [10] | ARM DEN<br>0073          | Network Camera Threat Model and Security Analysis (English language Protection Profile)                                                                                                |

| [11] | ARM DEN<br>0074          | Water Meter Threat Model and Security Analysis (English language Protection Profile)                                                                                                   |

| [12] | ARM DEN<br>0075          | Asset Tracker Threat Model and Security Analysis (English language Protection Profile)                                                                                                 |

| [13] |                          | NIST Special Publication 800-90A Recommendation for Random<br>Number Generation Using Deterministic Random Bit Generators                                                              |

|      |                          | NIST Special Publication 800-90B Recommendation for the Entropy<br>Sources Used for Random Bit Generation                                                                              |

|      |                          | NIST Special Publication 800-90C Recommendation for Random Bit<br>Generator (RBG) Constructions                                                                                        |

| [14] |                          | NIST Special Publication 800-22rev1a: A Statistical Test Suite for the<br>Validation of Random Number Generators and Pseudo Random<br>Number Generators for Cryptographic Applications |

| [15] | Commercial National Security Algorithm Suite. (superseding NSA Suite<br>B Cryptography)            |

|------|----------------------------------------------------------------------------------------------------|

| [16] | SEC - Recommended Elliptic Curve Domain Parameters                                                 |

| [17] | GlobalPlatform TEE Protection Profile Specification v1.2                                           |

| [18] | NIST Special Publication 800-108 Recommendation for Key Derivation<br>Using Pseudorandom Functions |

| [19] | NIST Special Publication 800-57 Part 1 Revision 4 Recommendation for Key Management                |

| [20] | NIST Special Publication 800-107 Recommendation for Applications<br>Using Approved Hash Algorithms |

| [21] | Common Methodology for Information Technology Security Evaluation 3.1                              |

| [22] | NIST FIPS PUB 202 SHA-3 Standard                                                                   |

| [23] | IETF RFC 8032 Edwards-Curve Digital Signature Algorithm (EdDSA)<br>Algorithms                      |

| [24] | OG-IS Crypto Evaluation Scheme Agreed Cryptographic Mechanisms                                     |

| [25] | IPA/ISEC: JCMVP: Approved Security Functions                                                       |

| [26] | Office of State Commercial Cryptography Administration, P.R. China                                 |

### **Terms and abbreviations**

This document uses the following terms and abbreviations.

| Term | Meaning                                  |

|------|------------------------------------------|

| ACL  | Access Control List                      |

| AES  | Advanced Encryption Standard             |

| АРВ  | Advanced Peripheral Bus                  |

| API  | Application Programming Interface        |

| AXI  | Advanced eXtensible Interface            |

| CMAC | Cipher-based Message Authentication Code |

| DMA  | Direct Memory Access                     |

| DPM  | Debug Protection Mechanism               |

| ECC  | Elliptic-Curve Cryptography              |

| ECU   | Electronic Control Unit                  |

|-------|------------------------------------------|

| EIP   | External Interface Peripheral            |

| НМАС  | Hash-based Message Authentication Code   |

| НИК   | Hardware Unique Key.                     |

| IDAU  | Implementation Defined Attribution Unit. |

| IPC   | Inter-process communication              |

| JTAG  | Joint Test Action Group                  |

| MCU   | MicroController Unit                     |

| MPU   | Memory Protection Unit                   |

| MTP   | Multiple-Time Programmable               |

| NSC   | Non-Secure Callable                      |

| NSPE  | Non-Secure Processing Environment        |

| NVM   | Non-volatile memory                      |

| OEM   | Original-Equipment Manufacturer          |

| ОТР   | One Time Programmable                    |

| OWF   | One-way Function                         |

| PE    | Processing Element                       |

| PSA   | Platform Security Architecture           |

| RMA   | Return Material Authorization            |

| RoT   | Root of Trust                            |

| ROTPK | Root Of Trust Public Key                 |

| RSA   | Rivest-Shamir-Adleman                    |

| SAU   | Security attribution unit.               |

| SHA   | Secure Hash Algorithm                    |

| SM    | Security Model                           |

| SoC   | System-on-Chip                           |

| SPE   | Secure Processing Environment            |

| SPM   | Secure Partition Manager                 |

| SWD   | Single Wire Debug                        |

|       |                                          |

| ТА   | Trusted Application                |

|------|------------------------------------|

| TDES | Triple Data Encryption Standard    |

| TEE  | Trusted Execution Environment      |

| TLS  | Transport Layer Security           |

| TMSA | Threat Model and Security Analysis |

| TRNG | True Random Number Generator       |

| TRTC | Trusted Real-Time Clock            |

### Feedback

Arm welcomes feedback on its documentation.

#### Feedback on this book

If you have comments on the content of this book, send an e-mail to arm.psa-feedback@arm.com. Give:

- The title (Arm<sup>®</sup> Platform Security Architecture Trusted Base System Architecture for Arm<sup>®</sup>v6-M, Arm<sup>®</sup>v7-M and Arm<sup>®</sup>v8-M).

- The number and release (DEN 0083 2.0 Beta 2).

- The page numbers to which your comments apply.

- The rule identifiers to which your comments apply, if applicable.

- A concise explanation of your comments.

Arm also welcomes general suggestions for additions and improvements.

# **1** Introduction [Informative]

Arm *Trusted Base System Architecture for Armv8-M* (TBSA-M) is an architecture for the design and implementation of secure devices.

The design of a secure product depends on analysis of threats to its assets through application use cases. The number and diversity of M-profile CPU-based products mean that, in practice, this approach might not scale. To address this, TBSA-M encapsulates best practice security principles when designing systems around Armv8-M *Processing Elements* (PEs).

These principles support the design and integration of the following features rooted in hardware:

- A Root of Trust (RoT).

- A Protected keystore.

- Isolation between Trusted and Non-Trusted software components.

- A Secure firmware update mechanism.

- A lifecycle management mechanism, for secure control of debug, test, and access to provisioned secrets.

- A high-entropy random number generator, for reliable cryptography.

- Cryptographic acceleration, so that real-time functionality can be maintained with the correct security properties.

TBSA-M is part of Arm *Platform Security Architecture* (PSA). PSA can be used to define a secure processing environment that isolates security-critical functionality and data from application software. This increases confidence in the trustworthiness of the device, even in the presence of exploitable software vulnerabilities. Arm PSA defines *Application Programming Interfaces* (APIs) for fundamental security functions. The APIs support the development of secure functionality that is more easily ported to other Arm-based platforms.

The goal of this document is to support the creation of platforms that support Trusted services. Trusted services are collections of operations and assets that require protection from the wider system, and from each other. This ensures their confidentiality, authenticity, and integrity.

This document aims to provide information that is useful to designers and implementers of secure platforms. This does not eliminate the requirement for security analysis during system design, despite the intention to reduce it. In addition, following the requirements and recommendations of this document does not guarantee that vulnerabilities will not exist in any compliant design.

TBSA-M describes a set of security requirements that assist the development of secure target systems. Among other uses, this set of requirements can support pre-silicon security design analysis within a company-specific secure development lifecycle. Some requirements have a clear architectural focus to support secure isolation partitions in a device as described in the PSA firmware framework. Other requirements are generic security requirements that represent good practice within the class of target systems.

TBSA-compliance is achieved when all requirements are either met or deemed not applicable. A Requirement may be deemed not applicable when the threats that the requirement mitigates is documented as countered in another manner or that those threats are demonstrated as not present in the specific threat model for the device. Security design reviews should compile evidence on each requirement that might be helpful in achieving PSA certification.

TBSA-M recommendations are provided as default design choices. Documenting which recommendations are followed, and which are not, is not required as part of the process of establishing TBSA-M compliance. However,

in some cases documenting which recommendations are followed may benefit the security design review. This documentation may form part of the compilation of evidence to support claims of adherence to, for example, relevant national security standards or market certification regimes.

### 1.1 Scope

This version of the TBSA-M specification is targeted at connected *microcontroller SoCs* (MCUs) and their product use cases, for example IoT. The MCUs have an Armv8-M, Armv7-M or Armv6-M processor as its host, and have sufficient security features to authenticate a boot process and ensure confidentiality and integrity of its data.

Implementations compliant with TBSA-M are sufficient to operate within the PSA *Security Model* (SM), which allows deployment of secure services using devices with known security properties

### **1.2 Organization of the document**

The document is organized in eight chapters in addition to this Introduction. Chapters 2, 3 and 4 describe the context in which subsequent requirements should be understood. Chapter 5 provides a set of requirements that TBSA-M compliant devices are expected to meet, together with a brief commentary about each requirement. Chapter 6 contains recommendations for how lifecycle management may be implemented, and Chapter 7 lists approved cryptographic algorithms for which hardware support is prescribed in Chapter 5. The Appendix tabulates the requirements in Chapter 5 for ease of access and to support design reviews.

Some chapters are labelled **Normative**. These chapters are prescriptive and are expected to be followed to comply with the architecture – subject to threat-model-based exemptions which should be documented at the security design review stage.

Other chapters are labelled **Informative**. These chapters are descriptive and are intended to help the reader to understand the concepts presented in the normative chapters and to provide reasonable defaults for certain design choices.

# **1.3 Target Platforms**

The target platforms that are addressed by this document are primarily IoT devices and automotive ECUs. These devices typically have several of the following product features:

- A long active lifespan.

- Resource constrained.

- A location that makes secure manual updates difficult.

- Potentially good physical access for untrusted third parties.

- Deployment in vast quantities.

This document concerns SoCs that are centered on Armv6-M, Armv7-M and Armv8-M PEs and embed non-volatile storage.

In general, these SoCs:

- Are closed systems so that the software running on them can be controlled.

- Have wired or wireless network connectivity.

- Support internal non-volatile bulk storage, most commonly embedded flash (eFlash).

• Integrate One Time Programmable (OTP) non-volatile storage for storage of assets provisioned at manufacture and later.

Given the variety of platforms and products that are covered by the scope of this document, each with a specific set of use cases, assets and threats, several aspects of this document are necessarily high-level.

However, the resulting collection of use cases, assets, threats, and necessary security measures cannot be reduced to a single, simple checklist of security requirements. Each platform requires specific analysis to determine the appropriate use of security features and will need to consider the specification and certification requirements of the target market.

Attacks on systems continuously evolve, with the effect that old security defenses must be strengthened, and new security defenses must be implemented to maintain the required level of security. The requirements described in this document represent best practice at the time of writing. Some requirements are intended to strengthen the security guidance when compared to previous versions of this document and its predecessors. In all cases, the differences are in the degree of security that is provided, or that is demanded by other market specifications. The newer requirements described here are more resilient to certain types of attack.

### 1.3.1 Level of protection

The types of attack that this document addresses are primarily those in which the attacker deploys unsigned software, either locally or remotely, or by injecting faults. The motivation behind this type of attack is to steal proprietary information , disrupt device functionality, or both. Although hardware protection technologies can protect against direct access to sensitive information, it is still possible to acquire sensitive information from statistical analysis attacks. Therefore, for certain applications it might be necessary to design both hardware and software so that visibility of such information outside the device is restricted.

Lightweight hardware attacks are those achieved using commonly available consumer or hobbyist equipment. Attackers obtain physical access to the device, but do not have the equipment or expertise to attack within the integrated circuit package. For example, an attacker might attempt to attack the system by:

- Probing the signals around the SoC to:

- Read, modify or substitute external memory contents.

- Read, modify or substitute information on communications channels.

- Tampering with how the device is clocked, powered or reset to corrupt programmable states within the system.

- Tampering with the device pins, for example debug pins, to attempt to read, modify or substitute internal states or internal memory contents.

- Tampering with manufacturing-related test pins to attempt to read, modify or substitute internal states or internal memory contents.

TBSA-M requirements focus on protecting easily accessible interfaces, discouraging the use of class keys, and supporting software countermeasures to low-cost side channel attacks.

Finally, advanced hardware invasive attacks, in which the attacker has access to laboratory equipment that probes on to silicon metal layers, infers fuse settings, or performs differential power analysis, are out of scope for this architecture.

# 1.4 Security Development Lifecycle

A *Security Development Lifecycle* (SDL) is a structured methodology for the creation of products which incorporate secure practices during each stage of their design lifecycle.

An SDL establishes a series of processes, policies, and activities that expand a design lifecycle to improve product security. SDLs are normally customized to fit with the particular design flow of the organization that is performing the design. Table 1 shows some of the early outputs of an SDL:

#### Table 1: SDL outputs

| Artifact                                                      | Description                                                                                                                                                                                               |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Security Product<br>Requirements                              | These are application and usage-specific security requirements.<br>These requirements include certifications that are imposed by the<br>market, and certifications whose need comes from the application. |

| Threat Modeling                                               | This identifies assets and threats at architectural level and microarchitectural design level. Relevant threats are determined using market requirements, vulnerability and risk analysis.                |

| Security Objectives                                           | These are high-level, descriptive countermeasures that mitigate the in-scope threats for identified vulnerabilities. Security objectives include assumptions about the operational environment.           |

| Security Functional<br>Requirements and Non-<br>requirements) | These are Security Objectives mapped to specific mechanisms (low-<br>level, prescriptive), which are to be implemented in the design.                                                                     |

These outputs mean that:

- Design specifications include security requirements.

- Design and verification reviews need to cover security requirements.

- Verification plans need to include security verification.

- Project reviews and stage gates need to consider progress in meeting security requirements.

- Errata need to be reviewed for security impact.

This document supports these activities by listing and describing common security requirements that need to be met in secure designs that are based around Armv6-M, Armv7-M or Armv8-M PEs.

### 1.5 Compliance

A claim of compliance to TBSA-M is an evidence-backed assertion that the design meets all applicable requirements that are described in this document. The assertion is normally made by the design team and takes the form of documented output of a design review of the device. Arm recommends that this assessment is made as part of the SDL.

The design team shall confirm, for each requirement, whether the requirement is fulfilled. This confirmation shall include a brief description of why the design is compliant and references to the relevant detailed specifications. In general, requirements may not be applicable if the threats that they mitigate can be shown to not form part of the threat model of the device, or that any vulnerabilities that might result from not meeting a

requirement can be demonstrated to be mitigated in another way. In some cases, it will be necessary to provide stronger security than is anticipated by these requirements. In these cases, evidence shall be documented to support this approach alongside the requirement. The Appendix of this document includes a checklist to assist in this activity.

In several areas, TBSA-M provides recommendations. Where possible, these recommendations are provided to give guidance on reasonable default design choices. The threat model and functional requirements of the device is key in determining how requirements are met and which recommendations are followed. This is beyond the scope of this document.

### 1.6 Scope and intended Audience

This document is primarily intended for the use of chipset manufacturers who wish to claim compliance with ARM TBSA-M architecture requirements. Architects, designers and verification engineers can use this specification to support the process of certification against PSA with independent laboratories.

# 2 Trustworthy networked devices [Informative]

Threat modeling and security analysis often requires detailed and expert evaluation of devices and the context in which they operate. This includes their use-cases, the assets they protect, and the threats they may face. The quantity and diversity of IoT, and other areas in which TBSA-M will be used, means that this approach does not scale well for cost-optimized devices.

A common feature of TBSA-M systems is that their context is a network of devices connected via insecure links. TBSA-M focuses on support for Trusted devices engaging in authenticated communications using cryptographic protocols, for example *Transport Layer Security* (TLS).

The complexity of software deployed on such devices requires that software is renewable to patch exploitable vulnerabilities, reliability, or performance issues and to manage the available functions of the device. Fundamental to the security model is hardware support for security by separation of software components.

# 2.1 Use Cases

TBSA-M requirements are driven by two classes of use cases.

#### 2.1.1 Secure machine to machine communication

A trustworthy network must be able to establish and maintain secure communications between devices that have mutually verified the identity and state of each other over physically insecure channels. In general, this can be achieved (with hardware support) for several basic functions:

- Secure boot

- To ensure that only authenticated software can run on the device.

- Secure debug and test

- $\circ$  To ensure that only authenticated entities can debug the software and test the hardware.

- Control of device lifecycle

- To ensure that the protection of assets and the availability of device functions follows a prescribed and constrained path from manufacture to device disposal.

- Attestation

- To ensure that devices present reliable evidence to other parties about the software and lifecycle state it is running. These require provision of an attestation identity.

- Isolation

- To ensure that accessibility of the most Trusted assets is in proportion to the level of trust in the software that can access it, and to provide hardware support for management of the confidentiality of assets between different device stakeholders.

- Cryptographic algorithms

- To provide secure storage, computation and communication at a performance level appropriate for the device. Many cryptographic algorithms require support for true random number generation, provision of Trusted time and the secure provision of device credentials and certificates.

- Unique binding

- To ensure that application level keys, credentials, and other secret or sensitive data is uniquely accessible to a specific device when in a specific state.

In addition, most devices will need to provide some protection from hardware attacks, including countermeasures to probing of accessible interfaces or other low-cost physical tampering.

### 2.1.2 Secure firmware update

Significant device firmware should have updateable components which encompass parts of the device RoT all the way up to application software. The location and quantity of deployed TBSA-M devices means that updates should be achievable over a network without requiring physical intervention. This requires the following hardware resources, to ensure that update is performed securely:

- Provision of firmware integrity and authenticity keys.

- Support for approved cryptographic protocols for reception, validation, and installation of new firmware, including monotonic version counters and support for trusted time.

- Provision of non-volatile memory to hold new firmware images and audit logs.

- Resources and mechanisms to remain secure in the event of a failed update, for example, a failsafe backup or a mechanism of removal from Trusted services.

# 2.2 Security goal

The goal of the TBSA is to protect the Trusted services on a device from attackers who would benefit from a compromise.

No security implementation is flawless. The goal is to ensure that attacks are not worth the time and money required. TBSA-M aims to protect against the most common general attacks. TBSA-M does not protect against all types of attack. Depending on its target market, a device implementing the TBSA-M architecture might be required to meet stricter security requirements.

Prevention of the Non-Trusted World from being compromised is out of scope for TBSA-M. Also, TBSA-M does not prevent malware from executing in a rich execution environment that attempts to acquire sensitive user information by acting as a trustworthy entity.

TBSA-M does not address laboratory attacks in which devices are unpackaged and probed, or power analysis attacks in which the power consumption of the device is correlated with its processing activity to extract assets.

### 2.3 Security analysis

A number of threat modeling methodologies are suitable for TBSA-M devices. Within PSA, the *Threat Models and Security Analyses* (TMSA) specifications provide some examples of best practice (see [10],[11] and [12]).

# **3 Platform Security Architecture concepts [Informative]**

### 3.1 Security by separation

All use cases rely on the protection of the sensitive assets, for example private data, cryptographic keys, credentials, and firmware, from disclosure or modification. This is best achieved by limiting the firmware and hardware that has access to them and separating these assets from the application firmware and hardware.

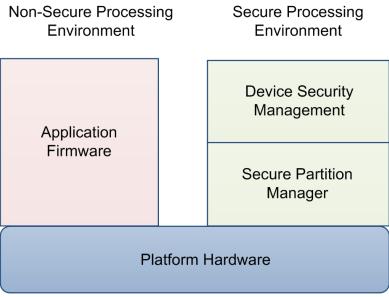

PSA comprises multiple building blocks to meet security objectives. The foundation of PSA is a separation of the system into a *secure processing environment* (SPE) for the sensitive assets and the code that manages them. The SPE is isolated from the *Non-secure Processing Environment* (NSPE), in which the main application and communication firmware executes. The *secure partition manager* (SPM) is the Trusted component within the SPE that is responsible for the isolation of the SPE and providing communication between the SPE and NSPE.

Faults or malicious activity within the NSPE should not compromise the behavioral integrity of the SPE.

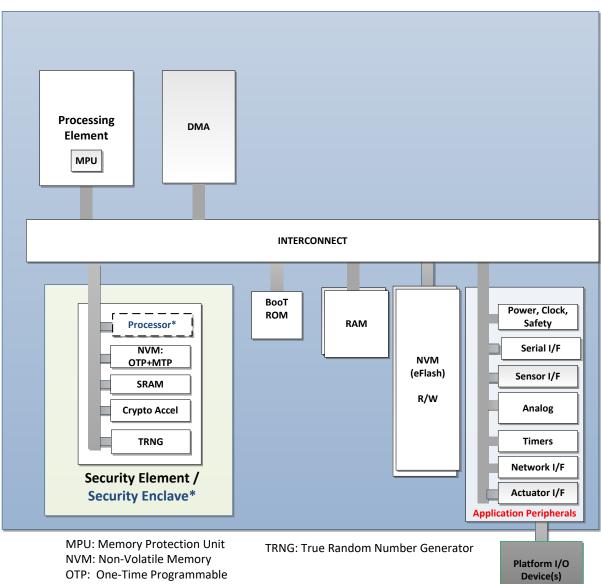

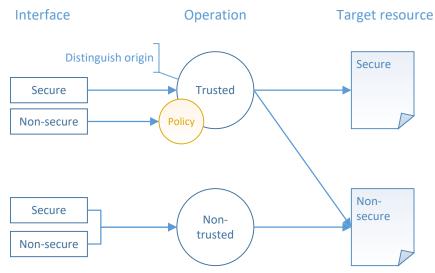

Figure 1 provides a high-level view of the structure defined by PSA:

#### Figure 1: Separation of the Secure Processing Environment

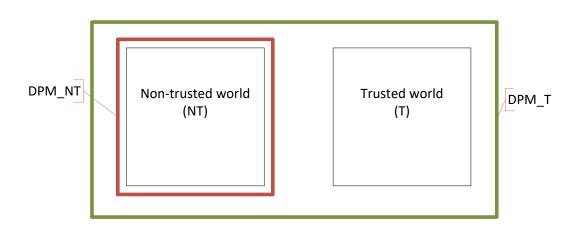

### 3.2 Trusted and Non-Trusted worlds

For Armv8-M-based devices, the separation provided by TrustZone into Secure state execution and Non-secure State execution gives rise to two worlds: the Trusted world, and the Non-Trusted world, respectively. The Trusted world is used by PEs executing in their Secure state or by peripherals acting on their behalf. Non-TrustZone processors are fixed to operate in one of the worlds. TrustZone processors can use secure transitions to operate in both worlds.

This document will use the term Trusted world to refer to hardware resources whose state supports the SPE and the term Non-Trusted world to refer to those hardware resources whose state supports the NSPE.

# 3.3 PSA software architecture

For many devices, secure remote device management services and application network management services will be provided by different organizations. Thus, adding secure device management services to a system not only increases the firmware complexity, but also adds another vendor whose product needs to be integrated in the device. This vendor's presence will increase integration complexity and cost.

Isolation of the sensitive assets further increases integration complexity. The secure device management firmware depends on the SPE design to execute the security-critical functionality in an isolated environment, and on the communication firmware used in the NSPE by the application.

PSA addresses some of this complexity by providing a standard SPE architecture and API for developing and communicating with firmware that runs within the SPE. PSA provides the specification of SPM and SPE, but not the implementation. Arm provides an open-source reference to implement these components as a separate product.

As an architecture, PSA enables alternative implementations of the SPE that address different quality-ofimplementation requirements for different parts of the IoT device market, while retaining the same programming model for securely isolated device functionality. For example, lighter-weight implementations are needed for more constrained MCUs and Partition Managers based on proven separation kernels for products that demand formal verification.

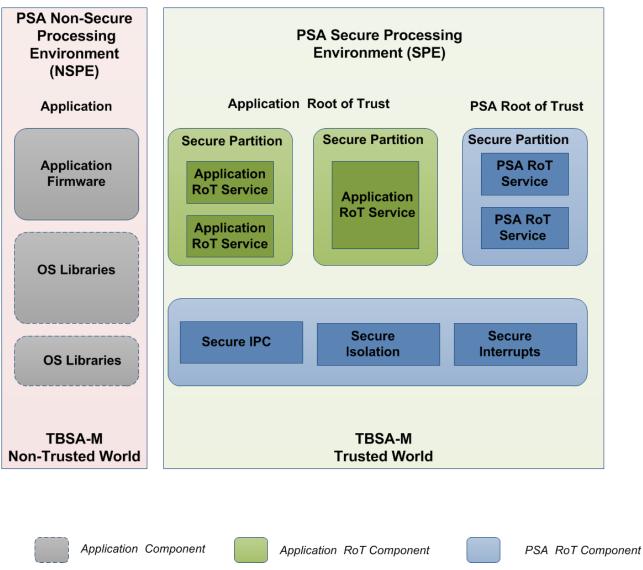

Figure 2 illustrates the mapping of the Non-Secure and Secure processing environments to the Non-Trusted and Trusted Worlds.

Figure 2: PSA Secure Processing Environment mapped to TBSA-M Trusted world

As described in Section 3.1, the PSA Security Model separates system processing into two domains: the NSPE and the SPE. The NSPE is typically much larger and includes the application firmware and OS kernel and libraries, and usually controls most I/O peripherals. The SPE includes the security firmware and those hardware resources that need to be isolated from NSPE firmware and hardware resources. A fundamental requirement of the Security Model is that NSPE firmware or hardware cannot inspect or modify any SPE hardware, code or data.

The PSA Security Model sub-divides the SPE into two sub-domains: the PSA *RoT* and the *Application RoT* (ARoT). The PSA RoT provides the fundamental secure services to the system and manages the isolated execution environment for the Application RoT secure services.

The PSA RoT comprises:

• A Security Lifecycle, which identifies the current phase of the device and controls the availability of device secrets and invasive capabilities, for example secure debug.

- An Immutable RoT, which is the combination of hardware and non-modifiable firmware and data installed during manufacturing.

- A Trusted Boot and Firmware Update, which ensures the integrity and authenticity of all secure firmware that runs on the device.

- An SPM, which implements the required isolation of the secure services, the *Inter-Process Communication* (IPC) mechanism that allows software in one partition to make requests of another, and scheduling logic to ensure that Partitions with requests to service are given execution time.

- A set of RoT services, which provides essential cryptographic functionality and manages access to the immutable RoTs for Application RoT services.

The PSA firmware framework [7] specifies the SPM, defines the runtime environment for RoT services and defines the standard interfaces for PSA RoT services.

# 4 Hardware supported isolation [Informative]

TBSA-compliant devices implement hardware to support the PSA isolation model.

Supporting the PSA isolation model gives rise to many architectural choices. For informative purposes, some of these are outlined in the following sections. Arm recommends that, where possible, a TrustZone-based system is implemented. TrustZone is known to provide a robust hardware framework when supported by a small amount of Trusted firmware. In addition, Arm provides significant design support for TrustZone-based systems that may not be available for other architectural choices.

### 4.1 TrustZone-based isolation

Processing Elements based on certain Arm architectures may support intrinsic isolation between secure and non-secure environments.

TrustZone for Armv8-M is a hardware-based security infrastructure that includes:

- An additional secure execution state of the processor including an MPU dedicated to this secure state.

- Secure interrupts.

- Secure debug.

- Infrastructure for propagating the security state of the processor to memory and peripherals, so that memory and peripherals are effectively isolated into secure and non-secure partitions.

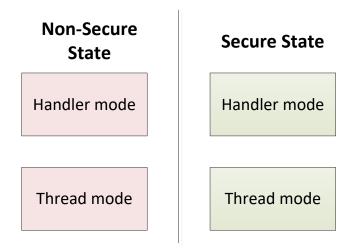

TrustZone for Armv8-M recognizes software as running in either the Secure or Non-secure state. These Security states are orthogonal to the existing Thread and Handler modes, and there is both a Thread mode and a Handler mode in both Secure and Non-secure state. Thread mode can also be either privileged or unprivileged. Figure 3 illustrates these states.

### Figure 3: TrustZone for Armv8-M adds Secure and Non-secure states to the operation of a PE

Similar to TrustZone in Cortex-A processors, code running in Secure state can access both Secure and Non-secure information, but Non-secure programs can only access Non-secure information.

TrustZone for Armv8-M is an optional architecture extension. By default, the system starts up in Secure state if the TrustZone Security Extension is implemented, as is required for TBSA-M.

TrustZone for Armv8-M is designed with small energy-efficient systems in mind. Unlike TrustZone in Cortex-A processors, the division of Secure and Non-secure states is memory-map based, and the transitions take place automatically, without the requirement for a Secure Monitor exception handler. This eliminates switching overhead.

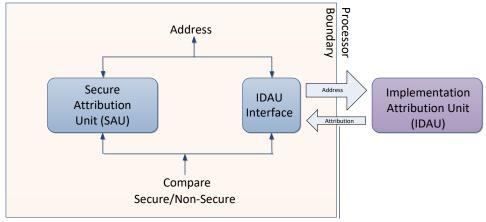

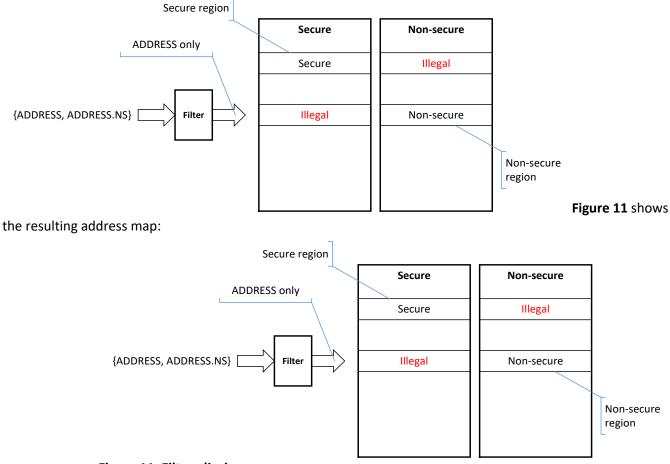

The designer of a microcontroller or SoC device must partition the memory spaces into Secure and Non-secure regions. Some regions are defined by software using a new unit defined by the Armv8-M architecture called the *Security Attribution Unit* (SAU), or by a device-specific controller logic connected to a special *Implementation Defined Attribution Unit* (IDAU) interface on the PE. The relationship between the attribution units is shown in Figure 4.

Figure 4: Security attribution defined by SAU and IDAU

The SAU is programmable in Secure state and has a programmers' model that is similar to the MPU. The SAU implementation is configurable by chip designers. The SAU should always be present, but the number of regions is defined by the chip designer. Alternatively, chip designers can use an IDAU to define a fixed memory map, and use an SAU optionally to override the security attributes for some parts of the memory. This is the recommended approach for TBSA-M devices.

The *Processing Element* (PE) state is dependent on the memory space definition. When the PE is running code in a Secure region, it is in the Secure state. Otherwise, it is in the Non-secure state. Application code can branch to, and call, code in the other Security domain, and the PE detects these switches automatically. Because an application can access functions in the other domain directly, TrustZone for Armv8-M is both flexible and simple to use.

The Secure memory space is further divided into two types:

- Secure: contains secure program code or data. This includes Secure stack, heap and any other Secure data.

- *Non-Secure Callable* (NSC): contains entry functions, for example, entry point for APIs, for Non-secure programs to access Secure functions.

Typically, NSC memory regions contain tables of small branch veneers. These are entry points. To prevent Nonsecure applications from branching into invalid entry points, a new instruction called *Secure Gateway* (SG) has been introduced. When a Non-secure program calls a function in the Secure side:

- The first instruction in the API must be an SG instruction.

- The SG instruction must be in a region attributed as secure and NSC by the SAU or IDAU.

There are many other security checking mechanisms within the Armv8-M architecture. Arm recommends the *Arm Architecture Reference Manual, Armv8, for Armv8-M architecture profile* for details.

In a typical TBSA-M compliant device, the host PE is only one part of the security system. Additional hardware is required to meet security requirements at a system level, to allow memory blocks to be partitioned into Secure memory regions and Non-secure memory regions. Similarly, access permission control logic is required to manage access permission of peripherals. Legacy peripherals and legacy bus masters are reused with appropriate bus wrapper logic.

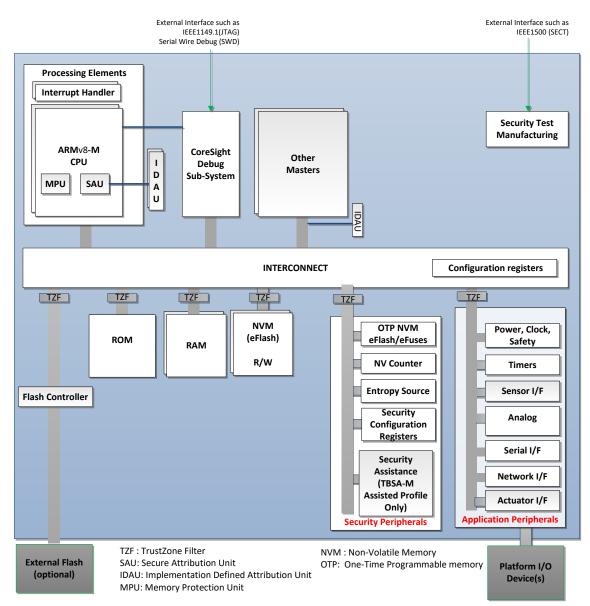

Figure 5 shows a typical SoC architecture based on TrustZone technology. The processor cluster is supported by several security hardware IPs that utilize TrustZone technology, for example the NS-bit, to work within the Trusted world.

Figure 5: Example TBSA-M system using TrustZone for Armv8-M

In a TBSA-M system using TrustZone for Armv8-M, TrustZone isolates the Trusted world from the non-Trusted world and provides the level-1 isolation (see Section 4.6).

Arm recommends deploying TrustZone for Armv8-M based solutions early in the design process, because PSA implementations using TrustZone for Armv8-M commonly provide robust and performant low-cost solutions with wide applicability.

# 4.2 MPU-based isolation

In a SoC that relies on MPU-based isolation, control of the *Memory Protection Unit* (MPU), is the primary means of isolation on an SoC, together with support for privileged execution on the processor. The separation of the Non-Trusted world and the Trusted world is provided by appropriate configuration of the MPU.

On this sort of platform, the PSA firmware framework uses a self-contained *Secure Partition Manager* (SPM) that creates independent security domains and provides hardware-enforced sandboxes, called partitions, for individual code blocks by limiting access to memories and peripherals. The SPM:

- Is initialized right after secure boot.

- Runs in the privileged mode of the processor.

- Sets up a protected environment using an MPU, for example the Arm Cortex-M MPU or a vendor-specific alternative. In particular:

- $\circ$  Its own memories and the security-critical peripherals are protected from the unprivileged code.

- Access Control Lists (ACLs) limit unprivileged access to selected hardware peripherals and memories.

- Allows interaction from the unprivileged code by exposing Supervisor Call-based APIs.

- Forwards and deprivileges interrupts to the unprivileged handler that has been registered for them.

- Prevents register leakage when switching execution between privileged and unprivileged code, and between mutually untrusted unprivileged modules.

- Forces access to some security-critical peripherals, for example *Direct Memory Access* (DMA), through Supervisor call-based APIs.

When using MPU-based isolation, the application and other parts of the NSPE run in the unprivileged processor execution mode and:

- Have direct memory access to unrestricted unprivileged peripherals.

- Can require exclusive access to memories and peripherals.

- Can register for unprivileged interrupts.

- Cannot access privileged memories and peripherals.

It is often difficult to run an application entirely in unprivileged state, because of restrictions on programs executing in this state. This means that significant parts of an application, with their accompanying vulnerabilities, might execute in a privileged state. Therefore, devices which rely solely on MPU and privileged execution for isolation afford the least robust implementations of PSA.

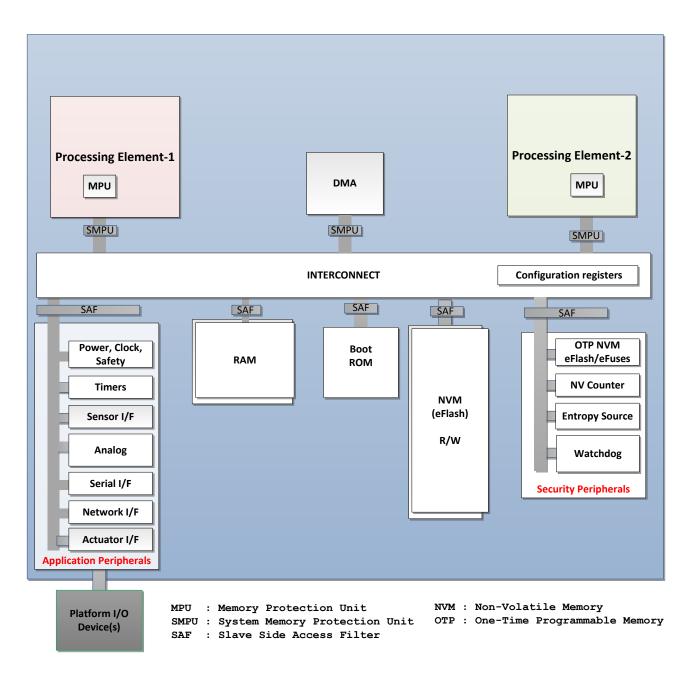

### 4.3 Dual PE-based isolation

It is sometimes convenient to dedicate one processing element to execute Trusted world firmware and to dedicate a second, different PE to execute Non-Trusted world firmware. This kind of design can provide sufficient isolation for a robust PSA implementation, together with suitable separation of requests, separate routing of interrupts and separation of debug. **Figure 6** illustrates this approach:

#### Figure 6: Example of a dual-CPU TBSA-M architecture

The separation between the worlds using dual PEs is supported by hardware in several ways. For example, a TrustZone-based system is functionally emulated by tagging bus requests and filtering them to ensure isolation between the Trusted and Non-Trusted worlds. Interrupts are statically hardwired to the core of the appropriate world. If more flexibility is required, then use a structure that routes some interrupts through a trusted interrupt controller first.

This arrangement allows more flexibility in deploying CPU performance. However, it typically uses more area and power than an equivalent single TrustZone-based CPU approach. Also, calls between firmware in the Trusted and Non-Trusted worlds will typically suffer higher latency in a dual-CPU approach.

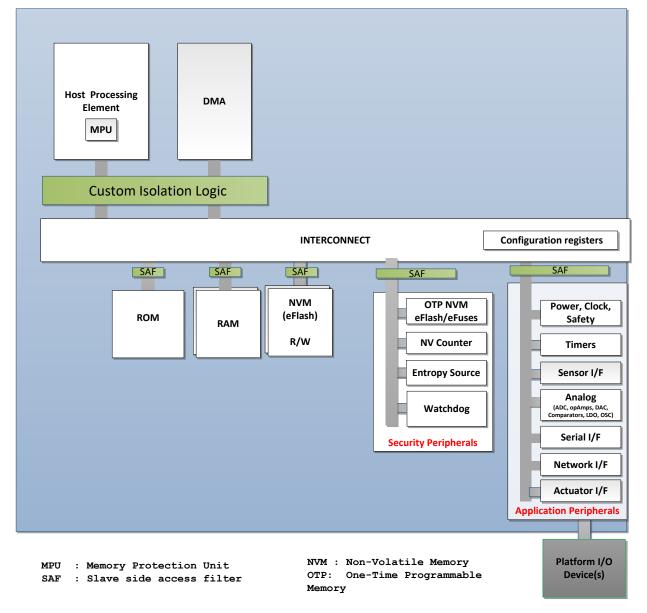

### 4.4 Custom-logic based isolation

Custom isolation logic is used to create generalized protection zones for SoC resources. In a protection zone, no access is granted to address regions, interrupts and debug for CPU execution contexts outside the zone. This mechanism can be used to separate the Non-Trusted world from the Trusted world and to provide a hardware foundation for PSA.

For example, custom logic is used to restrict memory access dependent on the PC of the instruction that made the access. Such logic is supplemented to isolate interrupts and debug access using master or slave-side filters that are configured by the Boot ROM prior to loading of the application firmware.

This arrangement allows PSA isolation to be built on top of the mechanism, provided the mechanism meets the security requirements outlined in Section 4.6. Figure 7 illustrates this SoC design:

Well-designed custom isolation logic can be very robust in protecting read-out of firmware IP by application software that is outside the firmware's protected zone. However, in general, care must be taken in the integration and security verification of such schemes within the firmware ecosystem and the extent to which such designs are re-used.

### 4.5 Trusted subsystems

Trusted subsystems are re-usable blocks of security IP that sit within the trust boundary of the PSA RoT. They provide RoT security services to the device. The PSA RoT attests their implementation and configuration. They may be integrated, or external and bound to the SoC. Examples include IP, for example DRAM protection systems, or Trusted Peripherals that support cryptographic operations, and Secure elements and Security Enclaves. In the case of Secure Elements and Security Enclaves, the subsystem implements its own local RoT and its own local security life cycle.

Security Elements are independent subsystems that provide a large set of RoT services for the device. Security Enclaves additionally integrate a processor on which it is possible to run application-specific firmware.

Figure 8 illustrates a TBSA system in which a Trusted subsystem, in the form of a security enclave, combines hardware accelerators, RoT control hardware with a layer of security middleware, and software tools for the IC and device production process.

MTP: Multiple-Time Programmable

#### Figure 8: Example of a TBSA SoC with an integrated security element/secure enclave

The security enclave provides:

- Cryptographic acceleration for the protection of data-in-transit and data-at-rest.

- Protection of various assets belonging to different, optional, stakeholders, for example IC vendors, device manufacturers, service operator or users). These asset protection features include:

- Image verification at boot/during runtime.

- o Authenticated debug.

- $\circ \quad \text{Random number generation.}$

- Lifecycle management.

- Provisioning of assets.

Trusted subsystems combine with one of the isolation mechanisms described in 4.1, 4.3 and 4.4 to make the divide more robust. See Section 4.8 for details.

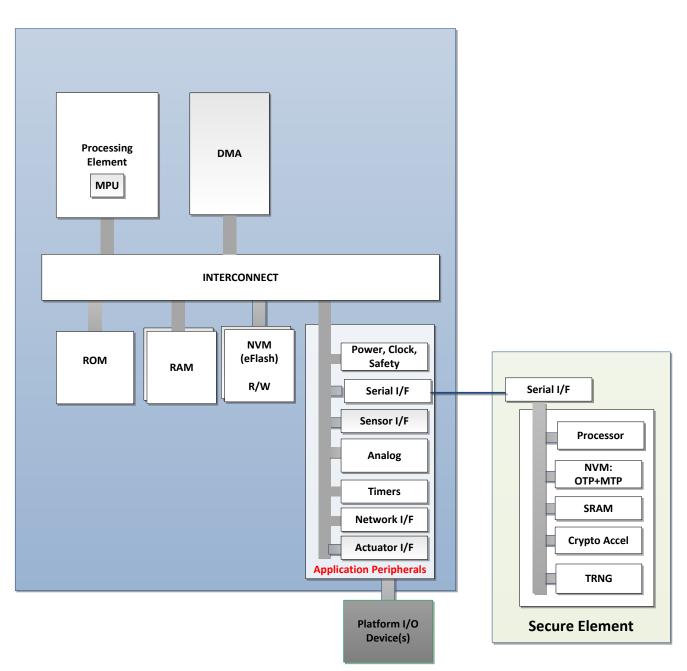

TBSA systems can also pair an SoC with an external secure element. Figure 9 illustrates this type of system. Depending on the application, a secure element may be used to:

- Support signature verification (for secure boot and firmware upgrade).

- Key storage and wrapping and unwrapping of local or remote keys.

- Generate on-chip key pairs.

- Establish a secure channel with a remote host including *Transport Layer Security* (TLS) handshake.

- Application usage monitoring with secure counters.

- Authenticate peripherals.

- Attestation.

It is essential to TBSA compliance that external secure elements robustly pair and create a secure channel with the host SoC. The secure element should reside within the Trusted world. See Section 4.6 for requirements.

Figure 9: Example of a simple TBSA-M SoC with an external security element

### 4.6 PSA isolation levels

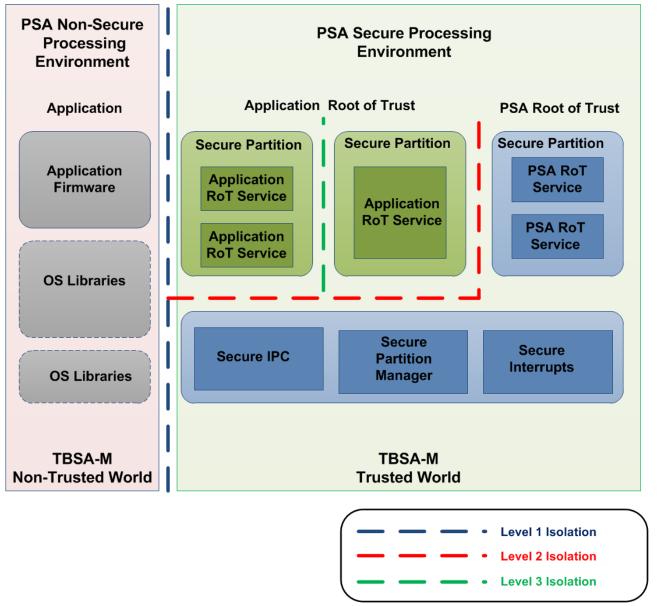

TBSA-M requires hardware support for isolation of software in accordance with the PSA firmware framework. Figure 10 illustrates the isolation levels:

#### Figure 10: PSA isolation boundaries

In PSA, the SPM is responsible for the isolation of the SPE from the NSPE, the PSA RoT from the Application RoT, and secure partitions within the SPE.

The isolation must be enforced by platform hardware throughout the system using master-side or slave-side filters, for example, the SAU and MPU in an Armv8-M CPU. This enforcement prevents other bus masters from

bypassing the isolation, and also mitigates software errors that are manifest in the NSPE from having the same effect.

The hardware filters that enforce isolation must be configured by the SPM or the secure boot firmware before the SPM runs. The filters must not be accessible to the NSPE or any Secure Partitions that are isolated from the SPM.

A PSA implementation fully isolates every secure partition, so that each partition only accesses its own data and peripherals, and only the SPM accesses the whole system.

Increased isolation improves the security and robustness of the system, by reducing its vulnerability to software defects. However, these benefits come at the expense of additional hardware, memory, performance or energy. The PSA Security Model specifies multiple levels of isolation, in order to support implementations with different security, performance and cost trade-offs. Table 2 below provides a summary of the three supported isolation levels:

| Isolation level | Description                                                                                                                                                                                                                                     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level 1         | SPE isolation                                                                                                                                                                                                                                   |

|                 | Two security domains                                                                                                                                                                                                                            |

|                 | SPE is protected from access by Non-secure application firmware and hardware                                                                                                                                                                    |

| Level 2         | PSA RoT isolation                                                                                                                                                                                                                               |

|                 | Three security domains                                                                                                                                                                                                                          |

|                 | In addition to Level 1, the PSA RoT is also protected from access by the Application RoT                                                                                                                                                        |

| Level 3         | Maximum firmware isolation                                                                                                                                                                                                                      |

|                 | Three or more security domains                                                                                                                                                                                                                  |

|                 | In addition to Level 2, each Secure Partition is sandboxed and only permitted to access its own resources. This protects each Secure Partition from access by other Secure Partitions and protects the SPM from access by any Secure Partition. |

#### Table 2: PSA isolation security levels

Arm recommends that RoT Service software that is to be placed in a secure partition is designed to run with Level 3 isolation and does not assume that data is shared with another Secure Partition or the NSPE. This design increases the portability of firmware to run on multiple PSA implementations and reduces the risk of introducing vulnerabilities related to the sharing of data.

Although the PSA firmware isolation levels are a useful indicator of the platform's security capability, it does not include all forms of isolation that the platform provides. Many platforms also use temporal isolation, in which resources are only available within a specific time window, for example, during boot. The additional security provided by Trusted Subsystems does not form part of the specification of TBSA-M, but may be used as countermeasure for a threat model posted by a particular application (see Section 4.5).

### 4.7 Basic architecture

The Basic architecture performs most of the security functions within Trusted world software on the host processor. It is supported by a minimum set of required security hardware, for example:

- Trusted Boot ROM.

- Trusted RAM, Trusted External Memory Partitioning, or both.

- Trusted peripherals:

- OTP Fuses, for secrets, counters, lifecycle states, etc.

- Entropy source.

- o Timer.

- $\circ$  Watchdog.

The Basic architecture ensures that the Trusted world software has access to all the assets it requires, and has the underlying mechanisms to protect the integrity, confidentiality, and authenticity of the Trusted world. The Trusted world software exports cryptographic services to the Non-Trusted world, and supports the execution of Trusted services by, for example, implementing an environment that can run Trusted applications.

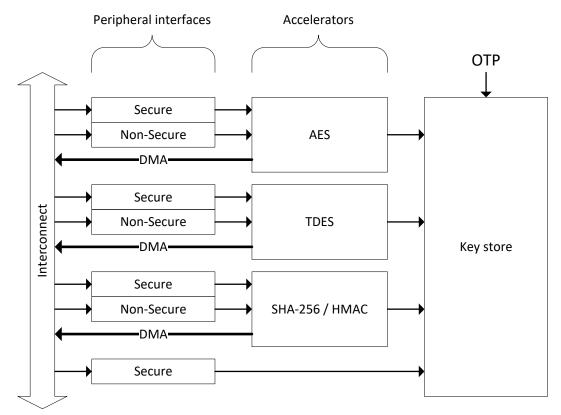

### 4.8 Assisted architecture

An Assisted architecture is a basic system that is supplemented with one or more Trusted subsystems. Assisted architectures may provide countermeasures which extend beyond the scope of TBSA-M.

An Assisted architecture builds on the Basic architecture by adding hardware to accelerate and offload some of the cryptographic operations from the Trusted world software, and to provide increased protection to high value assets, for example root keys.

The cryptographic accelerators support the most commonly used algorithms for encryption, decryption, and authentication, for example AES, TDES, SHA, RSA, and ECC.

Arm recommends increasing protection for the keys in the system by implementing a hardware Key Store. The Key Store enables use of the keys by cryptographic accelerators but prevents the keys from being read by both Non-Trusted and Trusted software.

Assisted architectures can also contain hardware for governing life-cycle state transitions and enforcing lifecycle state policies.

An assisted architecture may provide a hardware-initiated response to detect tamper events, as well as hardware countermeasures for:

- Invasive attacks, for example probing.

- Side channel attacks, for example power and electromagnetic emission analysis.

- Perturbation attacks, for example clock or voltage manipulation.

# **5 TBSA-M security requirements [Normative]**

TBSA-M requirements form a convenient checklist that can be used to support a pre-silicon security review of a design that is based on an M-profile processor. The requirements are based on principles of good security practice as applied to target platforms Section 1.3. Section 1.5 describes the significance of requirements and recommendations and what constitutes a claim of compliance for TBSA-M.

TBSA-M devices require support for PSA isolation levels.

R001\_TBSA\_BASE

The SoC must provide a hardware-based mechanism for separating the Trusted world from the Non-Trusted world.

This requirement supports PSA level 1 isolation (see section 4.6).

R002\_TBSA\_BASE The SoC must provide a hardware-based mechanism which is able to separate partitions within the Trusted world.

This requirement enables firmware to support PSA isolation level 2 and also enables firmware to support PSA level 3 isolation (see Section 4.6).

Arm recommends that SoCs provide a hardware-based mechanism so that secure partitions within the Application RoT are isolated from each other. This recommendation addresses PSA level 3 isolation. Examples of how R001 TBSA BASE and R002 TBSA BASE may be met are given in Chapter 4.

### 5.1 System view

At an abstract level, the TBSA-M is a system that comprises a collection of assets, together with operations that act on those assets. In this context, an asset is a data set that has an owner and a particular intrinsic value, for example a monetary value. All data sets are assets associated with a value, even if that value is notionally zero. A data set is any stored or processed information, including executable code as well as the data on which it operates.

High value assets that require protection should belong to the Trusted world, while lower value assets that do not require protection may belong to the Non-Trusted world. The actual classification, ranking, and mapping of assets to worlds depends on the target specifications, and is outside the scope of this document.

Similarly, an operation belongs to a world and is therefore classified as either Trusted or Non-Trusted.

R010\_TBSA\_BASEA Non-Trusted world operation must only access Non-Trusted world assets.R020\_TBSA\_BASEA Trusted world operation may access both Trusted and Non-Trusted world assets.

As described in Chapter 4, some TBSA-M architectures will be built around TrustZone for Armv8-M. In this case, code executing on an Armv8-M PE with the security extension exists in one of two Security states, Secure state or Non-secure state. Secure state corresponds to Trusted world operations, and the Non-secure state corresponds to Non-Trusted world operations. When in the Secure state, an Armv8-M PE with TrustZone can access state attributed as both Secure and Non-secure.

# **R030\_TBSA\_BASE** A SoC using TrustZone Isolation must be based on an Armv8-M architecture PE with the Security Extension and MPUs implemented.

In order to support common embedded OSs in a convenient manner, Arm recommends implementing both secure and non-secure MPUs, with each supporting a minimum of eight regions. Arm also recommends that the SAU is implemented, with a minimum of four regions. This is to give sufficient flexibility to implement common Armv8-M security attribution address map schemes.

Arm recognizes that the security features of a TBSA-M device will not be entirely implemented in hardware, and that the hardware might be configurable by software.

R040\_TBSA\_BASE The hardware and software of a TBSA-M device must work together to ensure that all the security requirements are met.

#### 5.2 Infrastructure

The TBSA-M is underpinned by a hardware infrastructure that provides strong isolation between the operations and assets of the Trusted and Non-Trusted worlds.

The processor is not the only key component of a larger SoC design that performs operations on stored assets within the wider system. In such a system, storage comprises registers, random access memory, and non-volatile memory. To provide the required protection for assets, the storage is divided, either physically or virtually, into two types: Secure and Non-secure. These types correspond to the Trusted and Non-Trusted worlds, respectively.

#### 5.2.1 Memory system

Operations and assets are connected by transactions, in which a transaction represents read or write access to storage containing the asset. Each transaction originates from either the Trusted world or Non-Trusted world.