The Top 5 Things to Know about Cortex-A12

IntroductionSmartphone and tablets are on the rise the increasing performance and convenience of these devices is definitely showing impact on the traditional PC market. Tablet sales will surge 53.4%, and PCs and notebooks will decline 11.2% in 2013,...

Introduction

Smartphone and tablets are on the rise the increasing performance and convenience of these devices is definitely showing impact on the traditional PC market. Tablet sales will surge 53.4%, and PCs and notebooks will decline 11.2% in 2013, according to recent figures released by Gartner.

With this explosive growth of mobile devices in the market, SoC vendors and OEMs are starting to segment into three tiers: premium, mid-range and a low-cost entry-level. Targeted solutions for each of those segments are key to deliver the best possible performance and efficiency at the right cost points.

The mid-range market specifically is a category where balance of performance/watt and die size is particularly crucial due to the cost pressure of such devices. Cortex-A9, initially the leader in high-performance SoCs, is currently the most popular choice within the mid-range market and is the shipping in volume since 2010.

Cortex-A12, released in June 2013, will set new performance levels within mid-range devices.

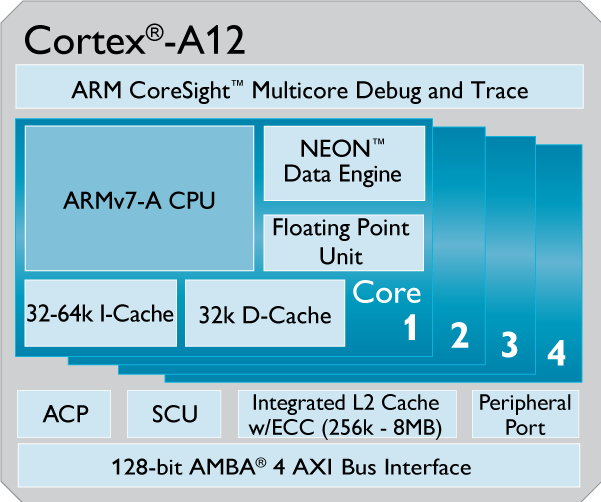

Figure 1: Cortex-A12 processor

Figure 1: Cortex-A12 processor

First sample silicon is expected by Q1 2014 and we will see volume shipments in end devices throughout 2014 and beyond – find below the top 5 things to know about Cortex-A12 before it hits the market:

1. Targeted at mid-range mobile devices

Cortex-A12 is the first mid-range solution specifically designed for this cost sensitive market. It features a new, ground up pipeline design, offering 11-stage full out-of-order 32b processing capabilities, and will deliver today’s high end feature sets in tomorrow’s mid-range devices – for lower cost and lower power consumption.

While the Cortex-A12 builds on the sweet spot identified by the Cortex-A9, Cortex-A9 was designed in it’s day (2008) to be a very high-end mobile processor – and delivered on that goal from 2010-2012 and it’s versatility allowed it to part of chip shipments of over a billion units!

2. Maximum 32-bit performance in the mid-range power envelope

Cortex-A12 is based on the 32-bit ARMv7-A architecture, today’s most popular architecture in mobile and delivers the highest 32-bit performance in the mid-range market.

Designed with the same power efficiency attributes as Cortex-A9, Cortex-A12 provides up to 40%+ additional IPC (Instructions executed per Cycle) performance. In other words, even when running at the same frequency, it will deliver 40% more performance. End devices that will use newer process technology and higher frequencies will deliver even higher performance upside.This additional performance, and the same state-of-the-art feature set as found in Cortex-A15 devices make Cortex-A12 an attractive upgrade option for any Cortex-A9 based SoCs. It is expected that 32-bit processors will remain the powerhouse for the mid-range market for several years to come.

3. Cortex-A9 heritage with a modern feature set

Cortex-A12 includes many new features but offers the same power efficiency and area efficiency as Cortex-A9. See below a feature comparison:

| Features | Cortex-A9 | Cortex-A12 |

|---|---|---|

| Architecture | ARMv7-A SMP extensions | ARMv7-A SMP / LPAE / Virtualization extensions |

| NEON-VFP | Yes (Optional) | Yes |

| GIC v2 | Yes (Internal) | External GIC |

| Integrated PTM | Separate Macrocell | Yes (Integrated) |

| L1 Instruction Cache | 16kB/32kB/64kB, 4-Way | 32kB/64kB, 4-Way |

| L1 Data Cache | 16kB/32kB/64kB, 4-Way | 32kB, 4-Way |

| L2 Cache | External - L2C-310 128kB to 8MB 8/16-way | Integrated 256kB to 8MB 16-Way |

| L2 Cache Protection | Optional Parity (SED) ECC external only | Optional ECC (SECDED) |

| Cache Line Size | 32 Bytes L1 and L2 | 64 Bytes L1 and L2 |

| AXI Bus Interfaces | 2 x 64-bit AXI 3 | 1 x 128-bit AXI 4 1 x 128-bit Peripheral Port |

| ACP Bus Interface | Optional 1 x 64-bit | Optional 1 x 128-bit |

| Physical Address | 32-bit | 40-bit |

Software developers will be happy to hear that programming for Cortex-A12 is getting even easier. Firstly, Cortex-A12 is fully code compatible to Cortex-A9 and features like the integrated L2 cache are fully transparent to software - no setup required.

Architecturally, Cortex-A12 provides extensions to enable new use cases not yet available on mid-range devices:

- Virtualization will help enable the BYOD (Bring-Your-Own-Device) trend and will allow a user to own one device, but use it independently for work and private purposes. The ability to run completely separate code depending on the use case keeps work related content securely separated from personal data – making life simpler for everyone.

- 1TB physical addressing (or LPAE) will allow your mobile devices to address more memory, so you can store and access larger data sets. Today’s mid-range mobile SoCs have sufficient memory addressing capabilities (up to 4GB) but with next generation Apps for gaming and high-definition movies requiring larger datasets, it is time to bring that capability into the mid-range.

4. Cortex-A12: It’s applicable well beyond mobile

Cortex-A12 is optimized for modern mobile use case but the performance, power efficiency and feature set of the processor, make it a perfect fit for other consumer electronics applications ranging from Digital TV, Set-top boxes or Home Networking to automotive infotainment applications. Many of these consumer devices today are based on Cortex-A9, and many partners are warmly welcoming this upgrade opportunity with Cortex-A12.

5. Interface flexibility and configurability is key

In addition to its outstanding power efficiency, Cortex-A12 has a number of dedicated interfaces that are particularly useful in the applications outlined above. Great examples are the Peripheral Port and the ACP port (Accelerator Coherency Port), both used to increase overall system performance:

- The Peripheral Port is mostly used to enable low-latency accesses to local peripherals like timers or interrupt controllers. This filters the peripheral traffic from the main memory (DDR) traffic and virtually eliminates traffic congestion between the two interfaces all leading to better performance.

- The ACP port allows for many use cases but is usually used to let external masters like DMA controllers participate in the cache coherency scheme of the processor cluster. This allows for a hardware based coherency management instead of a software controlled coherency mechanism and will speed-up overall performance.

Cortex-A12 is defined with the best possible feature set in mind, but still want our partners be able to fine-tune their implementations for their target use case. Cortex-A12 is delivered as configurable RTL that allows partners not to just select the number of processors, but attributes like TLB or cache sizes and inclusion/exclusions of features like secondary interfaces like Peripheral or ACP port in case they want to tailor the processor to their specific requirements.

Wrap-Up

Cortex-A12 is the latest A-class processor from ARM and has attracted many licensees who are designing SOCs for 2014 and beyond. It’s modern feature set and excellent power/performance attributes will see it deployed in millions of consumer devices over the next years. Who knows, it may even beat the time it took Cortex-A9 to get to that amazing one billion units shipped...

Re-use is only permitted for informational and non-commercial or personal use only.