Introducing the Arm AGI CPU 1OU Dual Node Reference Server

How Arm is unleashing rack-scale performance and efficiency for the agentic AI data center

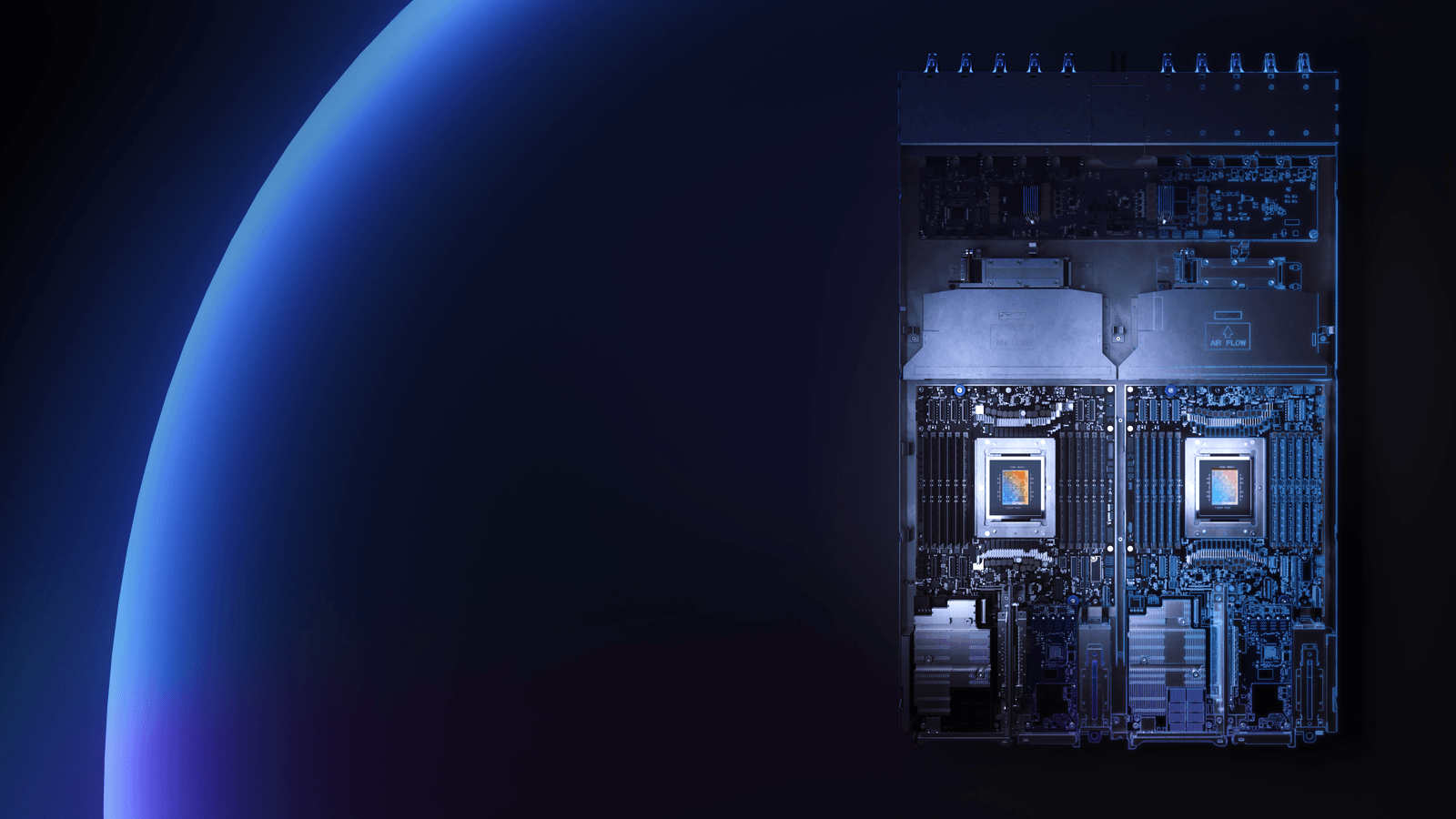

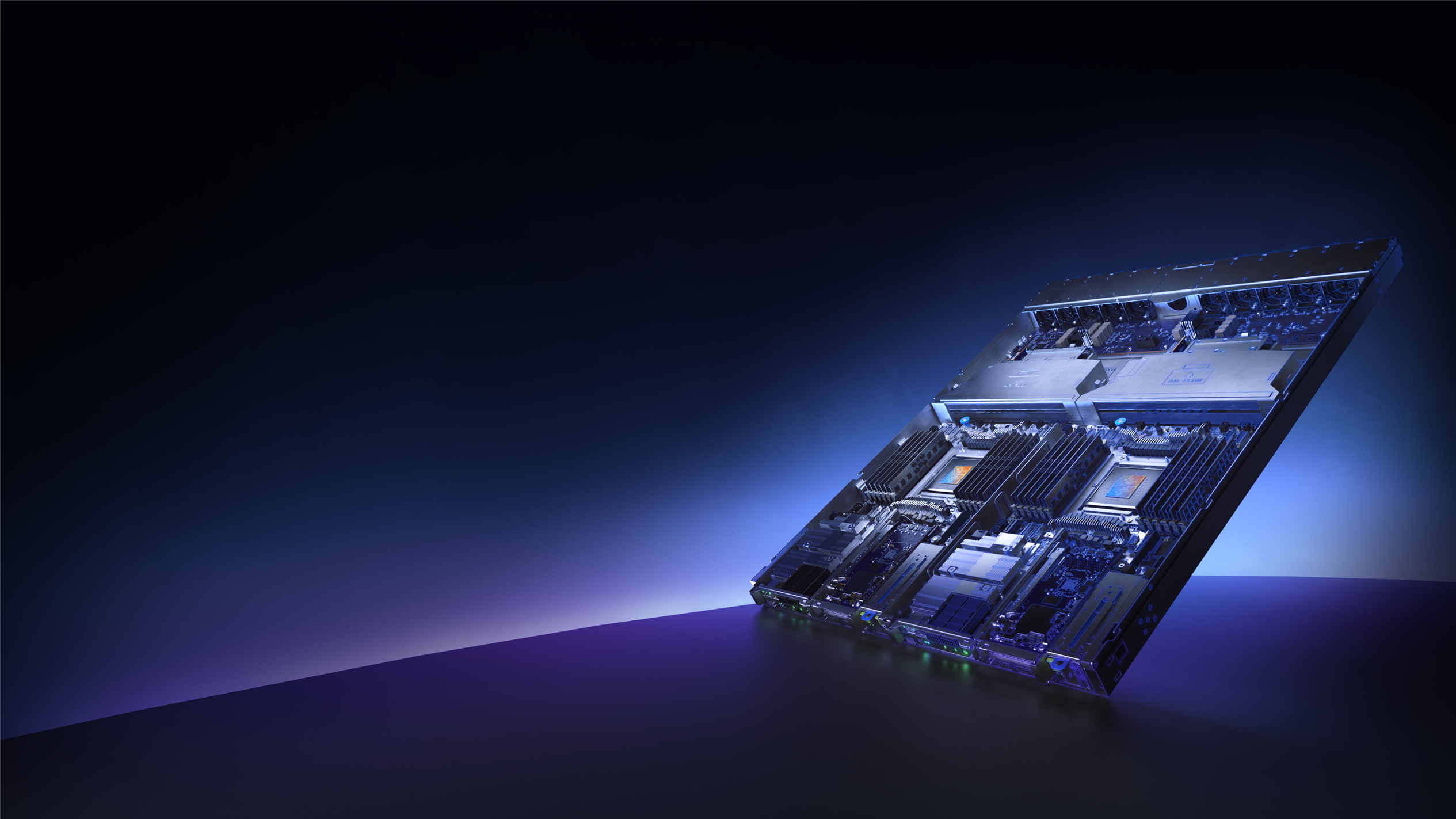

As part of today’s launch of Arm® AGI CPU, Arm’s first production-ready silicon product for the AI data center, we are introducing a modular, standards-based 1OU Dual Node Reference Server that brings the rack-first design philosophy of the Arm AGI CPU – built on the Arm Neoverse V3 architecture – to life. The reference server provides a production-representative environment for evaluating workloads, optimizing software stacks, and accelerating the deployment of next-generation Arm-based infrastructure.

As AI adoption accelerates, datacenters are entering a new phase. Cloud services are rapidly scaling and AI workloads are shifting from model training to broad deployment in commercial applications, increasingly driven by agentic AI use cases. To keep pace, infrastructure must deliver dramatically more compute and efficiency within fixed power, cooling, and space constraints.

Performance is no longer defined by a single server—it is defined at the rack level. Delivering more compute capabilities per rack, improving power efficiency, and maximizing infrastructure density have become the defining drivers of modern data center architecture.

Designed for rack-level deployment

The Arm AGI CPU 1OU Dual Node Reference Server takes a different approach. It is designed for rack-scale deployments as a dual-node server in a 1OU chassis, greatly increasing compute density per rack unit. This design philosophy influenced multiple aspects of the platform, including:

- Agentic-tuned performance: Up to 136 Neoverse V3 cores with class-leading 6 GB/s memory bandwidth per core at sub 100ns latency.

- Rack-scale architecture: 300W TDP enables deployment of up to 8160 cores per standard 36kW air-cooled rack compared to 500W x86-based deployments that need a 2U chassis.

- Unmatched compute density: More than 2x the performance-per-rack of comparable x86-based deployments.[1]

Why reference servers matter

Across the industry, silicon providers use reference platforms to provide a validated blueprint for system design and software enablement. These systems allow infrastructure partners to evaluate new silicon in a production-representative environment before building their own custom servers. Bringing a new platform to market requires a complete system environment that includes firmware, operating systems, memory, storage, networking, and system management.

A reference server acts as the starting point for production servers because it enables:

- Accelerated platform bring-up times: Developers can boot a variety of operating systems, deploy their software stacks, and begin working on platform-specific optimizations..

- Validated system architecture: Memory, I/O, storage, and firmware components are pre-integrated and tested.

- Performance evaluation: Partners can benchmark real workloads, measure power, and understand how the platform behaves for their use cases.

- Faster ecosystem development: OEMs/ODMs, operating system vendors and ISVs, as well as cloud providers, can all collaborate around a common platform.

And the new Arm AGI CPU 1OU Dual Node Reference Server achieves exactly that.

At the core: Arm AGI CPU

At the core of the platform is the Arm AGI CPU, a Neoverse V3–based processor designed for modern cloud and AI workloads. This translates nearly a decade of Neoverse infrastructure innovation into production-ready server silicon. Fabricated on TSMC’s advanced 3nm N3P process node, the Arm AGI CPU delivers up to 3.2 GHz all-core frequency within a 300W air-cooled envelope. This enables high compute density and exceptional performance-per-watt for modern AI and cloud workloads.

Arm AGI CPU integrates up to 136 high-performance Neoverse V3 cores with the Armv9.2 instruction set architecture (ISA), featuring dual 128-bit SVE2 (Scalable Vector Extension 2) units per core. These enable advanced AI and ML acceleration with support for bfloat16 and INT8 MMLA instructions. Operating at up to 3.2 GHz all-core clock speed (and 3.7 GHz boost), the Arm AGI CPU delivers strong per-core performance for latency-sensitive tasks, such as inference request handling and data preprocessing, and is designed to scale across AI inference, agentic AI, cloud-native compute, and a broad range of real-world enterprise workloads.

High memory bandwidth for data-intensive workloads

Modern workloads increasingly depend on moving large volumes of data efficiently through the system. The Arm AGI CPU integrates 12 DDR5 memory channels with up to 8800 MT/s DIMMs, providing more than 800 GB/s of memory bandwidth. This high-bandwidth memory architecture with 6 GBps/core allows the platform to sustain high throughput for workloads such as AI inference, large-scale analytics, and high-performance databases.

By reducing memory bottlenecks, the system enables better utilization of the CPU’s cores and supports the more efficient execution of data-intensive services.

Designed for heterogeneous compute to power agentic AI data centers

CPUs are the foundation of AI data centers and play a critical role in agentic AI, acting as the head node for an AI system through carrying out the following tasks:

- Coordinating the control plane;

- Scheduling and routing workloads;

- Managing IO;

- Handling networking and storage services;

- Enforcing security;

- Managing data orchestration between specialized accelerators; and

- Keeping the overall system balanced.

To support these heterogeneous environments, the Arm AGI CPU provides extensive high-speed I/O connectivity and a composable architecture via:

- 96 PCIe Gen6 lanes for accelerator, networking, and storage connectivity;

- Native CXL 3.0 support enabling memory expansion and pooling; and

- AMBA CHI Extension Links for future chiplet and accelerator-connected architectures.

These capabilities allow the CPU to act as the orchestration layer that coordinates data movement and workload execution across the entire system.

A modular platform built on open standards

The Arm AGI CPU 1OU Dual Node Reference Server is also designed to simplify system evaluation and platform development for Arm partners. It comes with a pre-validated, ready-to-use hardware and software framework for quick design and deployment, as well as workload performance evaluation. It adopts the Open Compute Project (OCP) and Arm SystemReady standards.

The server adopts the OCP DC-MHS architecture, a modular server design standard used by hyperscale data centers. This approach enables flexible system configurations while maintaining compatibility with modern data center infrastructure and, importantly, allows reuse of existing industry-standard components, such as OCP NIC and DC-SCM, reducing the need for custom platform design.

- A modular 1OU design compliant with the OCP DC-MHS (Data Center Modular Hardware System) specification.

- DC-MHS M-SDNO Class B305 1-socket 350W server board designed for a 21” ORv3 rack.

Arm’s SystemReady band compliance enables software runs across the ever-growing Arm Neoverse cloud platform. The Arm AGI CPU 1OU Dual Node Reference Server is targeting Arm SystemReady compliance – it runs the world’s biggest software ecosystem that runs out of the box, giving developers a familiar environment to access the Arm software ecosystem.

Scaling node density with a dual-node 1U design

The Arm AGI CPU 1OU Dual Node Reference Server adopts a dual-node (2N) configuration, enabling two independent compute nodes within a single 1U chassis operating at 1100W nominal power This design allows data center operators to double the nodes per rack unit, increasing overall compute density while maintaining the same physical footprint. For large-scale deployments, it delivers more cores per rack along with improved space utilization and infrastructure efficiency.

Each node features one Arm AGI CPU, 12 DDR5 DIMM slots, and robust PCIe Gen 6.0 expansion capabilities. Powered by PCle Gen 5.0 SSDs, storage is front and center, with each node supporting a combination of E1.S boot and data drives. There is also internal storage for additional expansion flexibility. The design comes with one NIC 3.0 card per node for high bandwidth networking connectivity, enabling efficient data movement across the rack and seamless integration into modern data center networks.

System management is delivered via a DC-SCM 2.1 module featuring the ASPEED AST2600 BMC. A standard set of front-panel I/O interfaces (USB 3.0, 1GbE, Micro USB, Mini DisplayPort) ensures easy debugging and access. Cooling is handled by dual rotor fans in a 19+1 redundant configuration. Finally, the system draws power through an OCP ORv3-compliant 48V bus bar, making it well-suited for modern data center infrastructure. Full details can be seen in the table below.

Arm AGI CPU 1OU Dual Node Reference Server

|

|

Arm AGI CPU 1OU Dual Node Reference Server |

|

SKU |

RS113021S-2 |

|

Chassis |

1OU ORv3 Chassis, (W) 21.14 x (H) 1.76 x (D) 31.7 inch (= 537 x 44.7 x 805 mm) |

|

Host Processor Module |

DC-MHS M-SDNO Class B |

|

CPU |

(2) Arm AGI CPUs |

|

Memory |

12x DDR5 64 GB 8000 MT/s (1DPC) |

|

Storage (Front) |

(1) E1.S 15mm Data Drive PCIe Gen 5.0, 7600 1.92TB (1) E1.S 9.5mm Boot Drive PCIe Gen 5.0, 7600 1.92TB |

|

Storage (Internal) |

(2) E1.S 9.5mm Data Drive PCIe Gen 5.0, 7600 1.92TB (2) E1.S slot available for expansion |

|

PCIe Expansion Slots (Front) |

(1) PCIe x16 FHHL Card, (1) HHHL (1) OCP NIC 3.0 per node |

|

PCIe Expansion slots (Back) |

(1) PCIe x16 FHHL Gen 6.0 expansion slot (1) PCIe x16 HHHL Gen 6.0 expansion slot |

|

I/O Ports |

(1) Micro USB Type B (1) Mini Display Port (1) 1Gbe Dedicated LAN Port (1) USB 3.0 |

|

TPM |

TPM 2.0 on DC-SCM module |

|

DC Power |

ORv3 48V Bus Bar |

|

System Fans |

(10) 4056 Dual Rotor fans (19+1 redundancy) |

|

System Management |

OCP DC-SCM 2.1 module with BMC Aspeed 2600 |

|

NIC |

OCP NIC 3.0 support |

|

Operating conditions |

Operating temperature: 5°C to 40°C Non-operating temperature: -40°C to 70°C |

|

Rack Support |

21” ORv3 Rack air cooled |

|

Server Power |

1100 W |

Fully validated system with quality you can trust

From signal integrity simulations to hardware stress testing, the Arm AGI CPU 1OU Dual Node Reference Server has been built and validated to industry standards. The system undergoes rigorous margining on both PCIe Gen6 and DDR5 interfaces. Eye diagram tests, voltage/timing validation, and compliance checks are all part of the standard qualification process.

Thermally, the platform has been designed to sustain the 350W SoC even under 40°C ambient conditions. Reliability testing includes hot/cold cycling, humidity endurance, operational load testing (OLT), and vibration/shock assessments, all to ensure robustness in real-world deployments.

The platform also includes test points, debug headers, and bring-up diagnostics to assist firmware and silicon validation teams.

Silicon lifecycle (SLC) management is a key part of fleet management. With the launch of the reference server, Arm is also introducing the new Arm System Diagnostic Tools, a modern set of SLC health management tools to detect, diagnose, and prevent system problems, like Silent Data Corruption (SDC) conditions, before they begin to impact workloads. Stress and Stability test modes enable smooth deployment of hardware and SDC and SLT modes ensure the fleet keeps running.

From hardware platform to development environment

Arm’s approach goes beyond delivering performant hardware;it’s about enabling a full-stack developer experience across cloud and on-prem environments. As part of this, Arm is continuing to invest in tooling that makes performance analysis and optimization on Arm more accessible and actionable for developers.

This includes upcoming capabilities that bring together system- and hardware-level insights with guided analysis, helping developers more easily identify bottlenecks across CPU, memory, and overall system behavior. These efforts build on Arm’s broader software strategy to simplify migration, validation, and optimization on Arm-based platforms — ensuring developers can move to Arm and achieve production-ready performance with confidence. This week Arm began previewing an upcoming performance tooling release called Arm Performix. With general availability coming soon, this marks a key a milestone for Arm developer software success, and it is just the beginning.

More details will be shared soon on arm.com.

A growing ecosystem of industry partners

The Arm AGI CPU is supported by a growing ecosystem of hardware and software partners.

Arm has worked with industry suppliers to establish an Approved Vendor List (AVL) covering key system components such as memory, storage, and networking. This ensures that customers can source validated components with confidence.

In parallel, leading server manufacturers, including ASRock Rack, Lenovo and Supermicro, are actively developing and validating production systems based on the Arm AGI CPU, providing customers with a path to broader customization and deployment support.

Every server needs Firmware. We have partnered with AMI to ensure their industry-standard Aptio BIOS and MegaRAC OneTree BMC products, together with open-source reference implementations of EDK2 and OpenBMC, create a robust foundation for innovation and operational excellence throughout the industry.

To support software developers and ISV partners interested in evaluating this platform, Arm is actively collaborating with leading Linux distributions from Canonical, Red Hat, and SUSE to ensure certified support for the production systems. In addition, developers can build and run their workloads with a mature software ecosystem of over 1000+ open source and commercial software packages enabled on the Arm architecture.

Design package, tools, and customer support

To accelerate development, Arm provides comprehensive documentation and a design package. This includes full schematics, layout files, SI/PI models, power and thermal profiles, firmware guides, and installation documentation. BIOS and BMC bring-up procedures are included for teams integrating custom firmware or extending platform capabilities.

Customers also gain access to onboard debug tools, training resources, and a growing self-service knowledge base. Whether you are deploying your first Arm-based server or integrating Arm AGI CPU into a larger platform, support is available at every step of the way.

Accelerating the next generation of infrastructure

The Arm AGI CPU 1OU Dual Node Reference Server represents an important step in enabling next-generation AI infrastructure built on the Arm compute platform. By designing both the silicon and the reference platform with rack-scale deployment in mind, the Arm AGI CPU enables infrastructure providers to deliver higher compute density, better power efficiency, and lower operating costs across modern data centers.

Moreover, by combining high-performance Arm server silicon with a modular, standards-based platform and a fully enabled software stack, the system provides developers and partners with everything they need to explore, evaluate, and deploy Arm-based infrastructure at scale.

Whether you are designing custom infrastructure, optimizing workloads for Arm-based systems, or building the next generation of AI-capable cloud services, the Arm AGI CPU 1OU Dual Node Reference Server provides a strong compute foundation to move forward.

Explore. Optimize. Deploy. With the Arm AGI CPU 1OU Dual Node Reference Server.

To learn more, visit Arm AGI CPU

Glossary

|

Acronym |

Expansion |

Description |

|

OCP |

Open Compute Project |

Industry consortium driving platform standardization |

|

DC-MHS |

Data-Center Modular Hardware System |

Modular, interoperable architecture for servers |

|

SDNO |

Scalable DeNsity Optimized |

Standardized form-factors for HPM |

|

1OU |

1 Open Unit |

Standardized measurement used in server and rack design to define vertical space, used in OCP designs |

|

DC-SCM |

Data-Center Secure Controller Module |

Decoupled module for server management and security |

|

BMC |

Baseboard Management Controller |

Decoupled processor running server management and security functions |

|

NIC |

Network Interface Card |

PCIe card providing Ethernet, FC network functions |

|

DPC |

(DDR) DIMM per Channel |

Increase amount of DDR memory supported |

|

UEFI |

Universal Extensible Firmware Interface |

Standardized firmware – EDK2 is an open-source implementation |

|

OpenBMC |

|

Open-source software project for BMC |

|

OEM/ODM |

Original Equipment/Design Manufacturer |

Ecosystem partner building production-grade servers |

|

IBV/IFV |

Independent BIOS/Firmware Vendor |

Ecosystem partner building production-grade firmware stack |

|

OSV |

OS Vendor |

OS/Distro (Linux or Windows) provider |

Footnotes:

Re-use is only permitted for informational and non-commercial or personal use only.