Advancing Chiplet Innovation for Data Centers: Novatek’s CSS N2 SoC in Arm Total Design

Novatek’s CSS N2 SoC, built with Arm Total Design, drives AI, cloud, and automotive innovation with chiplet-based, scalable compute.

By Marc Meunier

This blog is co-authored by Dr. Daniel Ping, Assistant Vice President, Novatek and Marc Meunier, Director Hardware Ecosystem, Infrastructure, Arm.

Novatek has successfully completed an Arm Neoverse CSS N2-based SoC through the Arm Total Design program, showcasing their capabilities to develop advanced datacenter chiplet-based compute on advanced node technology. Under the Arm Total Design program, Novatek was able to get access to Arm Neoverse CSS to develop the test chip, lowering risk, accelerating development cycles and delivering ecosystem-wide innovation to meet the surging demands of AI, cloud, and automotive markets.

With first silicon successfully returned in September 2025, Novatek has transitioned from design to execution, fueling validation, ecosystem enablement, and customer engagements. This momentum reflects both Novatek’s ASIC expertise and the collaborative power of Arm Total Design.

Powering Modular AI Platforms with Arm Chiplet System Architecture (CSA) Integration

Novatek’s Arm Neoverse CSS N2-based chip demonstrates the promise of Chiplet architecture: scalable, modular platforms designed for today’s most demanding compute workloads.

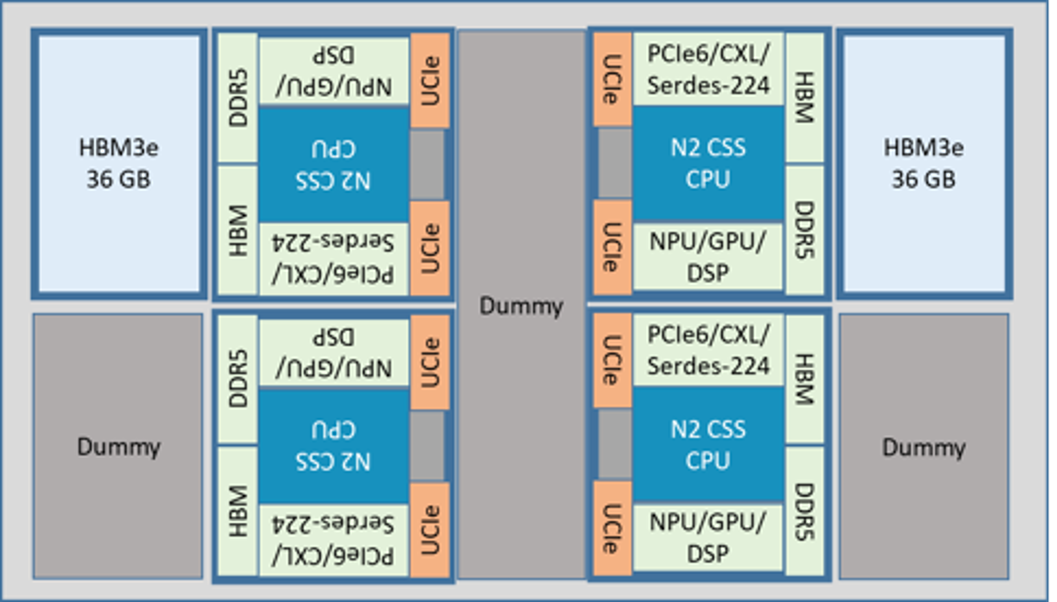

This chip integrated Arm Neoverse N2 CSS with DDR5/HBM3e memory controllers, PCIe6/CXL and 224G SerDes, effectively implementing a CSA “Compute 2 chiplet” that hosts application processors with direct access to system memory and I/O and is designed to interoperate with other chiplets via AMBA CHIC2C over the UCIe physical layer. The silicon boots a standard OS on the compute dies and exercises coherent links to peer chiplets, validating the feasibility of a CSA partitioned system and demonstrating readiness to design multidie chips.

Following CSA, we can minimize integration risk and fragmentation, shorten schedules through reusable, interoperable chiplets, and preserve coherency and security across dies via standard protocols. Future more, we can compose versatile ASICs by combining the compute chiplet with I/O and accelerator chiplets from a growing 60+ partner ecosystem to address diverse AI, HPC, and infrastructure workloads.

- Heterogeneous Integration: Combining NPUs, GPGPUs, DSPs, and accelerators to tailor performance for cloud AI, edge inferencing, and automotive applications.

- High-Speed Interconnects: Enabling massive bandwidth and low latency with UCIe 2.0, PCIe Gen6, CXL 2.0, SerDes 224G, DDR5, and HBM3e.

- Scalable Compute: Modular expansion across compute, memory, and networking adapts seamlessly to AI training, inference, and HPC.

- Silicon Success: The tape-out and return of CSS N2 silicon in September 2025 provides the foundation for validation and customer deployment — proving the Arm Total Design model delivers results.

Novatek’s CSS N2 SoC

Building AI-Grade SoCs with System Co-Development

Building AI-grade SoCs requires a system co-design approach. Novatek integrates advanced IPs and compute engines with pre-silicon validation to reduce risk and accelerate deployment.

- Server-Grade IPs: Integration of UCIe, HBM, DDR5, PCIe 6.0, CXL, and CPO for bandwidth-rich, scalable architectures.

- Compute Engines: GPGPUs, NPUs, DSPs, and accelerators connected via high-speed NoC interconnects for optimized data flow.

- Pre-Silicon Validation: Leveraging Arm Fixed Virtual Platforms (FVPs) and simulation tools for early firmware development and verification, ensuring first-time-right execution.

This approach underscores the Arm Total Design philosophy: collaboration accelerates innovation and makes advanced silicon deployment-ready faster.

Reliability, Security, and Standards

Novatek ensures that innovation is backed by trust, reliability, and compliance:

- Armv9-A Features: Memory Tagging, TrustZone, Virtualization, and scalability up to 128+ cores.

- System Certification: Compliance with Arm SystemReady SR, UEFI, and ACPI ensures compatibility, manageability, and automated deployment.

- Robust Validation: Testing for signal integrity, power integrity, EMI/EMC, and thermal reliability, paired with advanced 2.5D and 3D chiplet packaging.

- Industry Compliance: ISO26262 for automotive and proven IP leadership in video, display, and system integration reinforce Novatek’s track record of deployment-ready solutions.

This foundation ensures Novatek’s SoC is not only powerful, but also trusted and scalable for adoption across markets.

Powering the Future with Arm Total Design

With expertise spanning front-end, back-end, and chiplet integration, Novatek is a key contributor to the Arm Total Design ecosystem. Their Neoverse CSS N2 based chip proves that ATD is not just a framework, it is delivering tangible silicon, real-world enablement, and ecosystem momentum.

By combining technical leadership with ecosystem collaboration, Novatek exemplifies how Arm Total Design accelerates innovation, reduces risk, and expands opportunities across AI, cloud, and automotive infrastructure.

This milestone demonstrates that advanced, AI-ready SoCs are no longer limited to companies with massive R&D budgets. Through Arm Total Design, Novatek shows how collaboration lowers risk, shortens time-to-market, and makes cutting-edge compute accessible to a wider ecosystem.

Join Arm and Novatek at Open Compute Project (OCP) Global Summit 2025

Join us at the Arm booth during the OCP Global Summit (Oct 13–16) to see how Novatek and Arm Total Design ecosystem are shaping the future of chiplet-based compute together.

By Marc Meunier

Re-use is only permitted for informational and non-commercial or personal use only.