The future of tooling from IP configuration to SoC verification

The modern SoC typically consists of billions of transistors and is normally designed with many modular IP blocks. Each of these blocks have been commercially licensed, developed or reused from previous designs. Integrating these components can be ti...

By Jim Wallace

The modern SoC typically consists of billions of transistors and is normally designed with many modular IP blocks. Each of these blocks have been commercially licensed, developed or reused from previous designs. Integrating these components can be time-consuming and error-prone, which is continually getting more complex thanks to:

- Increased system complexity: consumers are demanding even more functionality for their connected lives

- Smaller processor technology: technology has accelerated through 10nm and below (but with higher risks and lower yields)

- Increased consumer cycles: products are now often refreshed at 6-12 months (and this is only getting faster), which is driving silicon design cycles

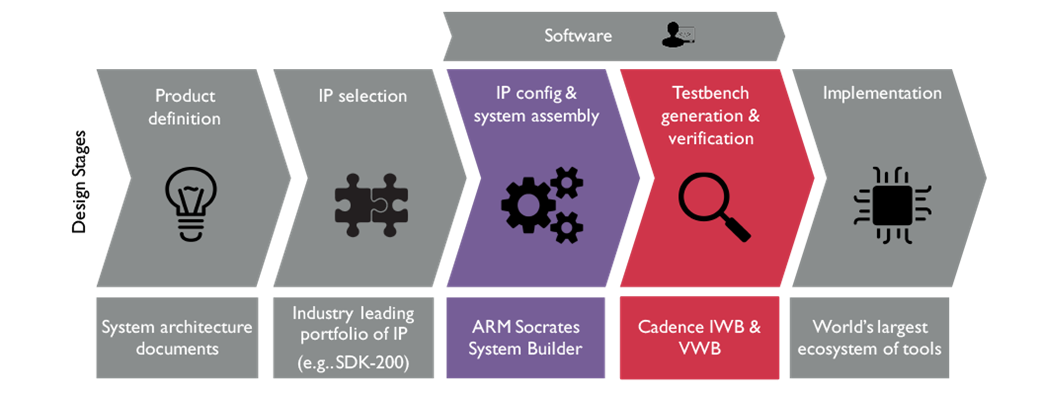

The design flow

A typical design flow will consist of several stages, which include:

- Stage one: product definition and IP selection

- Stage two: configuration, assembly, test bench generation and verification

- Stage three: implementation on the chosen process node before taping out to the fab

Figure 1: The system design flow

Figure 1: The system design flow

In the system assembly phase, designers have the significant challenge of stitching together these highly configurable IP blocks (which include processor cores, accelerators, interconnect fabric, plus debug and trace systems). In order to enable more efficient IP integration flows, the IP and EDA industry created IP-XACT [1]. IP-XACT uses IP metadata to describe, standardize and formalize IP interfaces. This allows the designer to treat these IP-XACT components as “lego blocks” that can easily fit together.

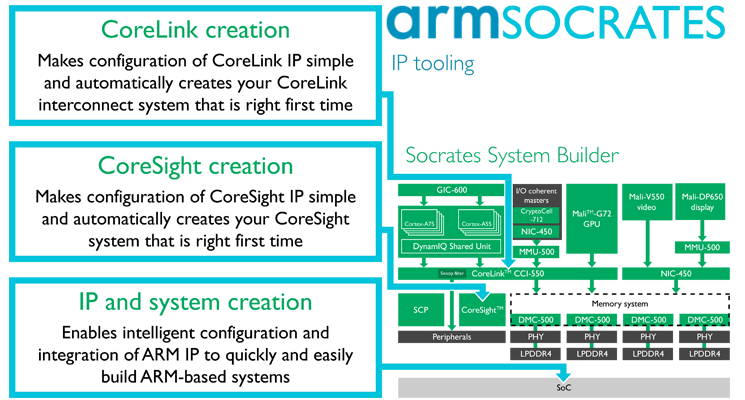

Socrates System Builder

Semiconductor companies also utilise a whole range of EDA and IP tools, to design and analyse their SoCs. These are essential to reducing time-to-market pressures and ensuring right first-time silicon. One of these tools, Socrates System Builder (which builds on 10+ years of heritage and hundreds of successful tape-outs), standardises, configures, and intelligently integrates third party IP with Arm IP, to create leading edge SoCs.

The System edition of Socrates System Builder is now available and will guide architects and designers through the configuration and creation of optimized systems. Socrates System Builder helps simplify the configuration of Arm CoreSight and CoreLink System IP and automatically create a CoreSight system & CoreLink interconnect that is right first time. It also includes the Arm IP Catalog, which helps users select and configure the IP using a Graphical User Interface, Command Line Interface or an API.

Figure 2: Arm Socrates System Builder

In summary, the tool provides users with:

- A state-of-the-art stitcher to stich IP together more efficiently and more accurately when compared to any other methods available on the market

- The ability to package IP from RTL and documentation into the IP-XACT standard format

- The capability to generate RTL for any level of hierarchical design (e.g. IP, system IP, subsystem)

- A tool to generate a design specification

Learn more about Arm Socrates System Builder

EDA partners, such as Cadence, also provide a complete suite of tools that complement Socrates System Builder, including test bench generation and verification.

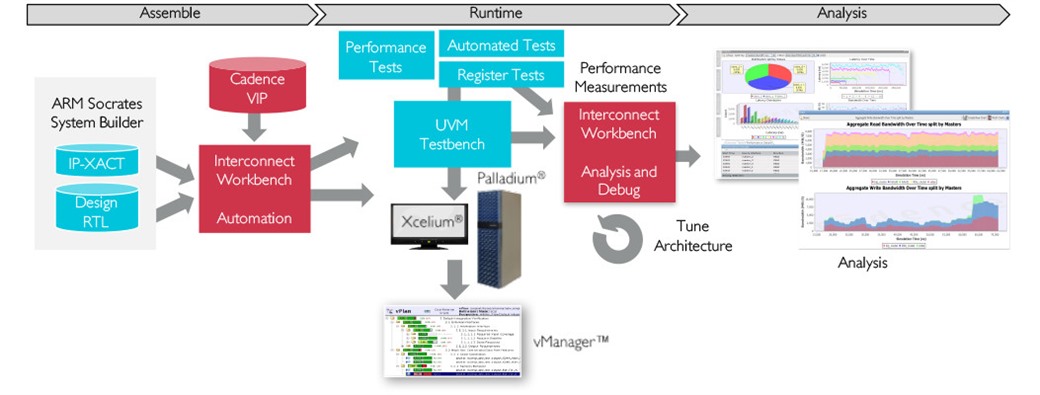

Figure 3: Cadence Interconnect Workbench (IWB) environment

Cadence Interconnect Workbench (IWB) takes in the automatically generated RTL and the IP-XACT metadata description from Socrates System Builder. It then builds either a performance-oriented or a verification-oriented testbench. The solution works with Cadence Verification IP and executes on the Cadence Palladium® Enterprise Emulation Platform and the Xcelium Parallel Simulator, with coverage results collected and analysed in the Cadence vManager Metric-Driven Signoff Platform.

Demonstrating the future at DAC

These tools significantly reduce the time needed to implement and validate complex systems and help designers meet the ever-increasing needs of their customer. Come see this future at DAC, where Arm and Cadence have collaborated to make this possible. Use the IP Bocks to build and test your own mini system in the joint Arm-Cadence demo; if you’re the fastest you’ll be the proud owner of a new Fitbit Alta HR!

[1] IP-XACT - Approved as IEEE 1685-2009 on December 9, 2009, published on February 18, 2010.

By Jim Wallace

Re-use is only permitted for informational and non-commercial or personal use only.