From Cloud to Edge, Arm Artisan Physical IP Tuned for Trillion Intelligent Devices in Infrastructure Market

In this blog, read about physical IP and devices in the infrastructure market.

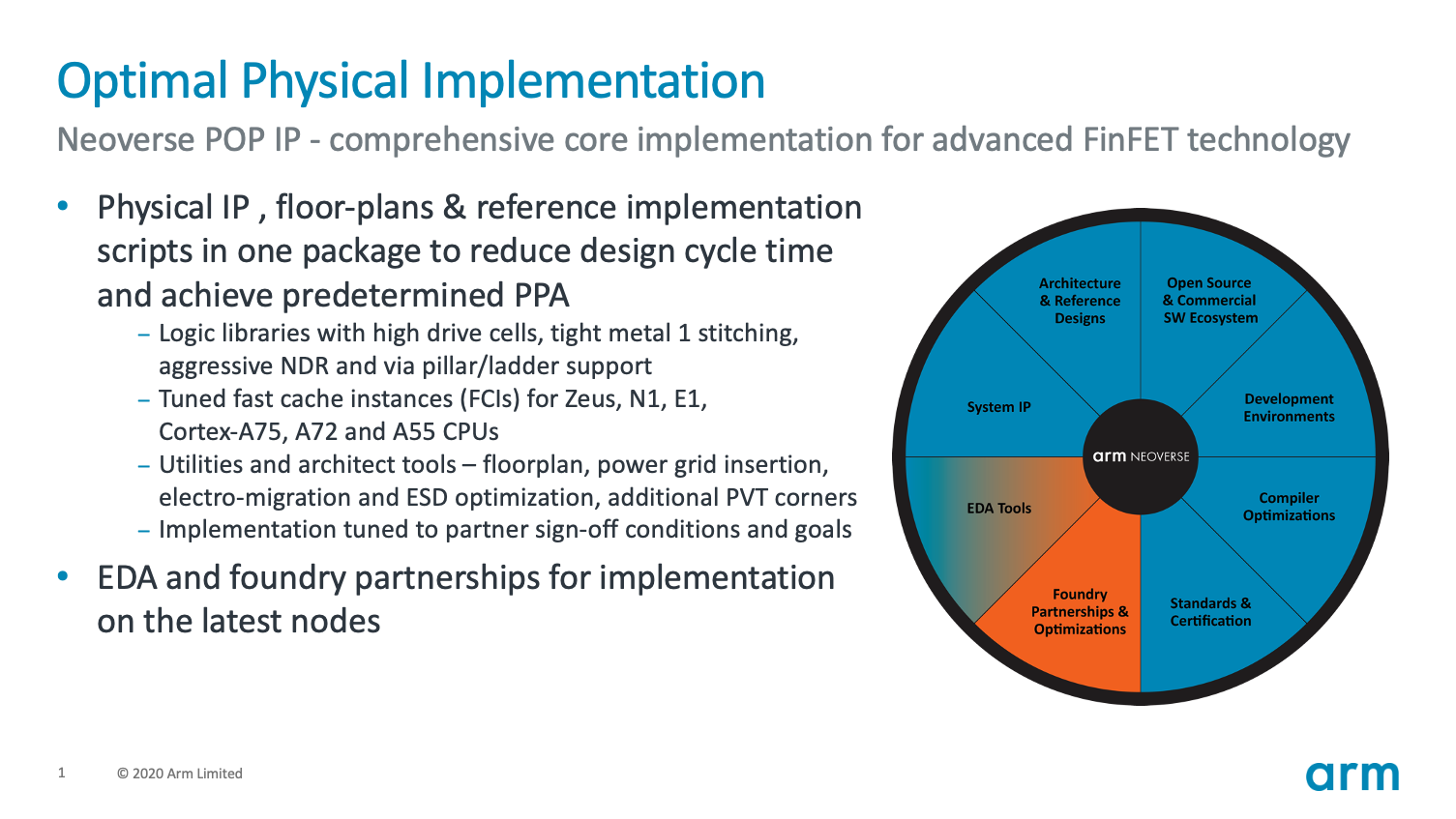

Physical IP, floorplans & reference implementation scripts in one package to reduce design cycle time and achieve predetermined PPA

Arm launched the Neoverse family in 2018, laying out a vision for Secure, high-performance, flexible cloud-to-edge computing built for a world of a trillion connected devices. Leveraging our proven success in the smartphone market and expertise in power-efficient CPUs, the Neoverse portfolio was the first extensive CPU core roadmap developed for the infrastructure market.

Since the debut of Neoverse, more than 50+ and increasing ecosystem partners have joined Arm on this journey. These partners created both hardware and software momentum as well as the successful infrastructure solutions. SiPearl, for instance, has signed a major licensing agreement with Arm to develop its first generation of microprocessors.

Neoverse platform enables SiPearl to gain nearly ten years of development and helps fine-tune for super computing

SiPearl is designing the high-performance, low-power microprocessor for the European exascale supercomputer. The agreement with Arm enables SiPearl to reap the benefits of the high-performance, secure, and scalable next-generation Arm Neoverse platform, codenamed “Zeus,ʺ as well as the robust software and hardware Arm ecosystem.

The Neoverse platform contains a wide range of CPU cores, CMN (Coherent Mesh Network) mesh interconnect, System IP and Artisan Physical IP which fulfills market requirements for high performance and energy efficiency.

Arm’s Artisan Physical IP portfolio is fine-tuned for infrastructure market targeting both high performance and highly efficient designs. The high-performance solutions include:

- High-speed standard cell architecture with multiple VT and channel lengths

- Dual rail Fast Cache Instances (FCI) with high-speed periphery and redundancy tailored to the specific CPU

- Ultra-wide PVT (process, voltage, temperature) range support from super-underdrive to super-overdrive voltages

- Neoverse POP IP and utilities to enable customers to replicate a floorplan and PPA (power, performance, area) characteristics.

The Arm Artisan physical IP portfolio also includes IP to manage power efficiency:

- High-density library architecture

- Power management and retention Kit

- Fast Cache instances with power gating and low-power periphery

- Analog IP to control voltage droop

- Neoverse POP IP

Neoverse POP IP targets high performance implementations in advanced node processes

Arm Neoverse POP IP is a comprehensive core implementation for advanced FinFET technology. POP IP was developed and tuned for the Neoverse platform and more particularly for supercomputing applications. Arm’s Physical Design Group is working closely with SiPearl team to fine-tune their POP specifications and signoff criteria. Goal is to meet their PPA targets and translating these numbers onto silicon.

Arm POP IP is a collaboration between physical IP designers and CPU RTL designers to develop a best-in-class PPA, shorten time to market and reduce design risk. It can be configured to allow both high-performance and power-efficient designs using logic IPs and FCIs in most advanced FinFET process nodes.

POP IP helps SiPearl solve new challenges when designing high-performance cores in advanced FinFET technologies. This includes analyzing EM/IR thanks to Power Grid Architect and Electromigration Generator utilities. Also managing stringent design rules and IP integration with a fully validated place-and-route flow. Finally Improving clock tree robustness by defining high drive cells associated with optimal VIA pillar and ladder and non-default rules (NDR).

Our Neoverse POP IP developed for SiPearl includes:

- Reference implementation flow from synthesis to signoff timing closure

- High-performance logic library including high drive inverters

- Fast cache instances

- Tight power grid

- VIA pillar and ladder definition

- NDR rules

- Power Grid Architect Utility for power grid insertion.

- Electromigration Generator Utility to control EM constraints

We are in the business of helping our partners succeed. Reach out to us to know more about physical IP and Neoverse POP IP for your design needs today. Or visit us at upcoming TSMC events.

We are ready, are you ready?

Re-use is only permitted for informational and non-commercial or personal use only.